# Untersuchungen zum Konzept der HADES Driftkammerauslese und Test der TDC - Prototypkarte

${\bf Diplomarbe it}$

von

Jörn Wüstenfeld

Institut für Kernphysik Johann Wolfgang Goethe-Universität Frankfurt am Main

Durchgeführt bei der Gesellschaft für Schwerionenforschung, Darmstadt

November 1997

# Inhaltsverzeichnis

| 1 | Ein | leitung                                           | 1  |

|---|-----|---------------------------------------------------|----|

| 2 | HA  | DES, das Dileptonenspektrometer @ GSI             | 3  |

|   | 2.1 | Konzept der Dileptonen - Identifikation           | 3  |

|   | 2.2 | Das HADES - Triggerkonzept                        | 5  |

|   | 2.3 | Aufbau des Spektrometers                          | 7  |

|   |     | 2.3.1 Magnet                                      | 7  |

|   |     | 2.3.2 Ringabbildender Cherenkov - Detektor (RICH) | 8  |

|   |     | 2.3.3 Flugzeit - Wand (TOF)                       | 9  |

|   |     | 2.3.4 Multiplizitätsdetektor (Shower)             | 9  |

|   | 2.4 | Die Vieldraht - Driftkammern                      | 9  |

|   |     | 2.4.1 Aufgabe                                     | 9  |

|   |     | 2.4.2 Aufbau                                      | 10 |

|   |     | 2.4.3 Funktionsweise                              | 11 |

|   |     | 2.4.4 Bestimmung der Driftgeschwindigkeit         | 13 |

|   |     | 2.4.5 Entstehung der Trackinginformation          | 14 |

|   |     |                                                   |    |

| 3 |     | slesekonzept der Driftkammern                     | 17 |

|   | 3.1 | Die Datenraten                                    | 17 |

|   | 3.2 | Das Konzept                                       | 18 |

|   | 3.3 | Die Komponenten                                   | 21 |

|   |     | 3.3.1 Analogkarten (Daughterboards)               | 21 |

|   |     | 3.3.2 Digitalisierung (Motherboards)              | 22 |

|   |     | 3.3.3 Auslesesteuerungseinheit (RC)               | 22 |

|   |     | 3.3.4 Konzentrator (SAM)                          | 23 |

|   |     | 3.3.5 Bustreiberkarte (DTR + DMA) $\dots$         | 23 |

|   |     | 3.3.6 Detektortriggereinheit (DTU)                | 23 |

| 4 | Rea | disierung des Konzeptes                           | 25 |

|   | 4.1 | Das Motherboard                                   | 25 |

|   |     | 4.1.1 Aufgabe des Motherboards                    | 25 |

|   |     | 4.1.2 Aufbau des Motherboards                     | 25 |

|   | 4.2 |                                                   | 27 |

|              |       | 4.2.1 Anordnung der Motherboards              |                 |

|--------------|-------|-----------------------------------------------|-----------------|

|              | 4.0   | 4.2.2 Bus zur Auslesesteuerungseinheit        |                 |

|              | 4.3   | Kühlung der Komponenten                       | 33              |

| 5            | Der   | HADES TDC - Chip                              | 35              |

|              | 5.1   | Anforderungen an den TDC                      | 35              |

|              | 5.2   | Der funktionelle Aufbau                       | 35              |

|              | 5.3   | Das Meßprinzip                                | 37              |

|              | 5.4   | Die Rechnerschnittstelle                      | 39              |

|              | 5.5   | Die Betriebsmodi des TDC's                    | 40              |

| 6            | Test  | s des TDC                                     | 43              |

|              | 6.1   | Problemstellung                               | 43              |

|              | 6.2   | Zu untersuchende Parameter                    | 44              |

|              |       | 6.2.1 Zeitauflösung                           | 44              |

|              |       | 6.2.2 Spannungsabhängigkeit                   | 44              |

|              |       | 6.2.3 Temperaturverhalten                     | 44              |

|              |       | 6.2.4 Differentielle Nichtlinearität          | 45              |

|              | 6.3   | Experimenteller Aufbau                        | 45              |

|              | 6.4   | Initialisierungs- und Ausleseprogramm         | 47              |

|              | 6.5   | Ergebnisse                                    | 48              |

|              |       | 6.5.1 Zeitauflösung                           | 48              |

|              |       | 6.5.2 Spannungsabhängigkeit                   | 49              |

|              |       | 6.5.3 Temperaturverhalten                     | 49              |

|              | 6.6   | Diskussion                                    | 50              |

|              |       | 6.6.1 Experimenteller Aufbau                  | 50              |

|              |       | 6.6.2 Zeitauflösung                           | 52              |

|              |       | 6.6.3 Spannungsabhängigkeit                   | 54              |

|              |       | 6.6.4 Temperaturverhalten                     | 55              |

| 7            | Zusa  | ammenfassung und Ausblick                     | 57              |

| Δ            | Ann   | nerkungen zur Physik des Halbleiters          | 59              |

|              |       |                                               |                 |

| В            | Kon   | nmandos der Prototyp Auslesesteuerungseinheit | 63              |

| $\mathbf{C}$ | C.1   | Problemstellung                               | <b>65</b><br>65 |

| D            | Initi | alisierungsregister des TDC's                 | 60              |

# Abbildungsverzeichnis

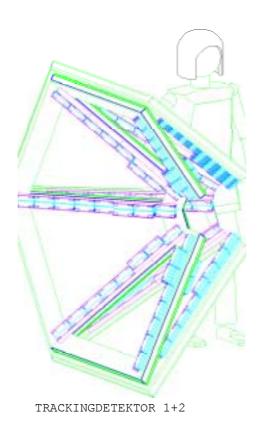

| 2.1  | Schnitt durch HADES                            |

|------|------------------------------------------------|

| 2.2  | Feldverteilung im HADES-Toroid                 |

| 2.3  | Aufbau einer Driftzelle                        |

| 2.4  | Driftkammeraufbau Ebene II                     |

| 2.5  | Driftkammersignal                              |

| 2.6  | Ankunftszeitverteilung                         |

| 2.7  | Feldverlauf in einer Driftzelle                |

| 2.8  | Teilchenspur in der Nähe eines Signaldrahtes   |

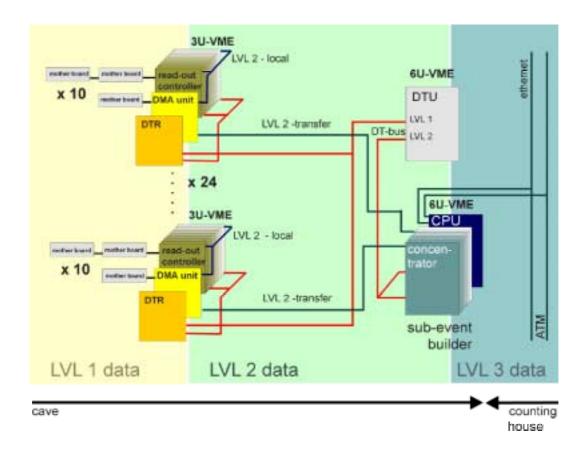

| 3.1  | Prinzip der Driftkammerauslese                 |

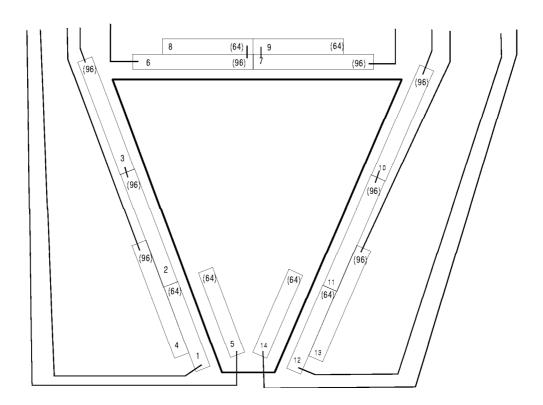

| 4.1  | Anordnung der Motherboards auf dem Detektor    |

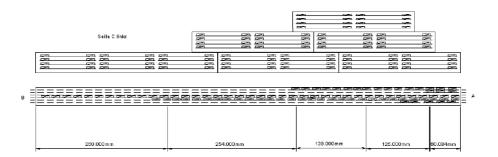

| 4.2  | Seitenansicht Driftkammerebene I               |

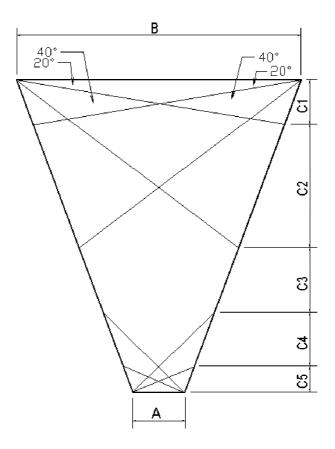

| 4.3  | Auslesezonen der Driftkammern                  |

| 4.4  | Bussysteme eines Driftkammermodules            |

| 4.5  | Busauslastung Driftkammerebene I               |

| 4.6  | Busauslastung Driftkammerebene II              |

| 5.1  | Blockschaltbild des TDC                        |

| 5.2  | Schaltbild des TDC Meßkreises                  |

| 5.3  | Blockschaltbild der TDC - Rechnerschnittstelle |

| 5.4  | Blockschaltbild TDC - Kette                    |

| 5.5  | Zeitdiagramm der TDC Initialisierung 41        |

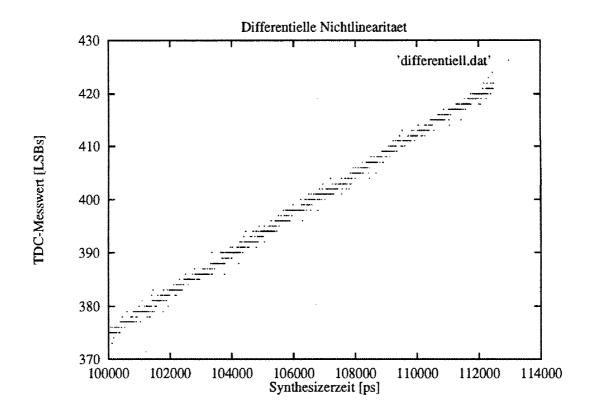

| 6.1  | Differentielle Nichtlinearität                 |

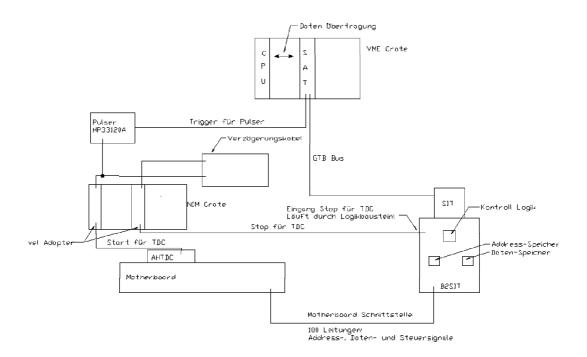

| 6.2  | Testaufbau                                     |

| 6.3  | Interne Kalibrierung                           |

| 6.4  | Zeitauflösung außerhalb des Spill              |

| 6.5  | Zeitauflösung im Spill                         |

| 6.6  | Spannungsabhängigkeit für 300 ns Verzögerung   |

| 6.7  | Spannungsabhängigkeit für 300 ns Verzögerung   |

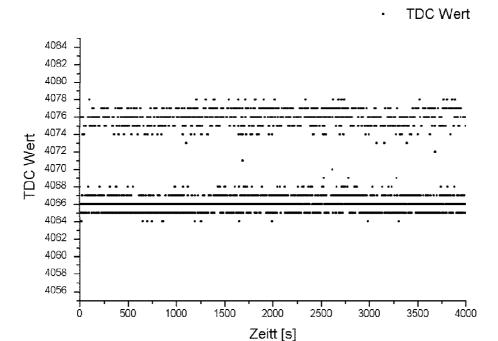

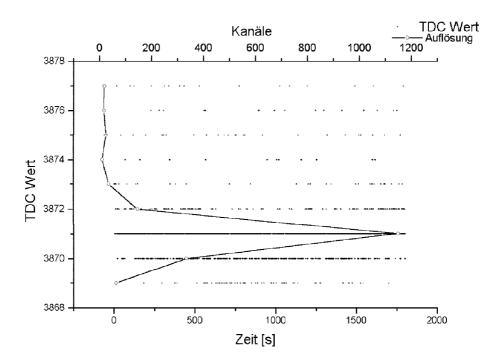

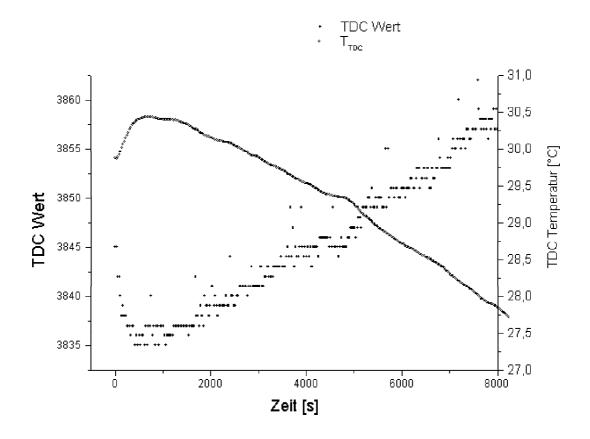

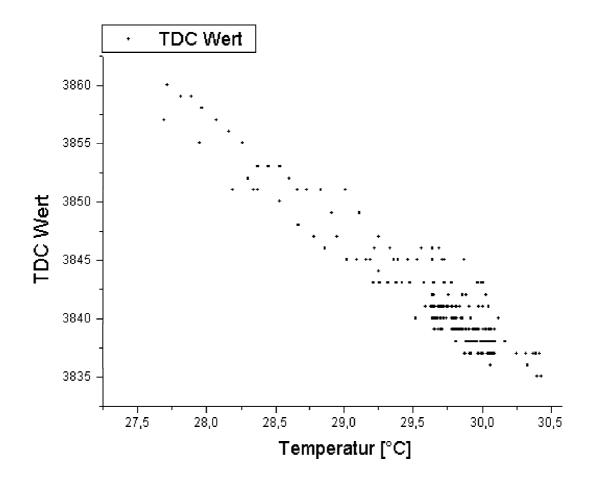

| 6.8  | Temperaturverhalten in einer Langzeitmessung   |

| 6.9  | Temperaturabhängigkeit der Meßwerte            |

| 6 10 | Relative Temperaturahhängigkeit 56             |

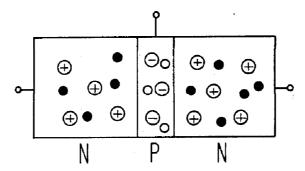

| A.1 | Prinzip des Aufbau eines biplolaren Transistors | 6( |

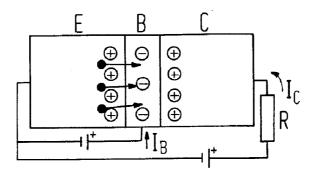

|-----|-------------------------------------------------|----|

| A.2 | Betrieb eines Transistors                       | 6. |

| A.3 | Prinzipschaltbild eines Inverters               | 6. |

# **Tabellenverzeichnis**

| 2.1 | Anzani der Signaldrante          | 11 |

|-----|----------------------------------|----|

| 3.1 | Parameter der Analogkarten       | 21 |

| 4.1 | Drahtanzahl pro Driftkammermodul | 30 |

| 5.1 | TDC Spezifikationen              | 36 |

|     | Adressen der B2SIT Karte         |    |

| C.1 | Klassen des TDC Testprogramms    | 67 |

|     | TDC - Steuerregister 0 und 1     |    |

# Kapitel 1

# Einleitung

Das Dileptonen - Spektrometer HADES (High Acceptance Di - Electron Spektrometer) wurde zum Nachweis von Elektron - Positron Paaren (Di - Leptonen) aus Kern - Kern - Stößen bei Einschußenergien um 1 AGeV konzipiert. Untersucht werden sollen die Eigenschaften von Hadronen bei Dichten, die das Dreifache der normalen Kerndichte erreichen können. Als Spektrometer der zweiten Generation konzipiert, sollen mit ihm auch die Messungen des Di - Leptonen Spektrometers (DLS) am BEVALAC (Berkley, USA) durch Messungen mit hoher Präzission erweitert werden. Daneben sollen auch Meson - Kern Stoßsysteme, z.B.  $\pi$  - Kern und Proton - Kern Stoßsysteme untersucht werden. Dies wird durch die Nutzung des  $\pi$  - Strahls möglich.

Die DLS Messungen ergaben, bedingt durch die eingeschränkte Akzeptanz und Massenauflösung, nur bei leichten Stoßsystemen Spektren von  $e^+e^-$ -Paaren mit hinreichender Statistik. Die geometrische Akzeptanz für  $e^+e^-$ -Paare von HADES wird mit 35% das Hundertfache der Akzeptanz des DLS betragen. Die Polarwinkelakzeptanz von HADES reicht von 18° bis 85° bei nahezu vollständiger Abdeckung des Azimutwinkelbereiches. Diese wird durch den Raumbereich, den die Spulen des Magneten einnehmen, beschränkt.

Zudem besitzt HADES mit einer angestrebten Massenauflösung von weniger als 1% im Massenbereich des  $\omega$ -Mesons gegenüber DLS (12%) eine deutlich bessere Möglichkeit zur Identifizierung schmaler Resonanzen und insbesondere zur Trennung der  $e^+e^-$  Beiträge von  $\rho-$  und  $\omega-$  Mesonen.

Zur Untersuchung der Eigenschaften heißer Kernmaterie eignen sich Dielektronen besonders, da sie nicht der starken Wechselwirkung unterliegen. Dadurch bleibt die Information über ihre Entstehung vollständig erhalten. Dies ist insbesondere dann vorteilhaft, wenn das Teilchen, aus dessen Zerfall sie stammen, noch in der Kollisionszone hoher Dichte und Temperatur, die auch als Feuerball bezeichnet wird, zerfällt. Dieser Feuerball zeichnet sich bei GSI Einschußenergien durch eine im Vergleich zum Grundzustand der Kernmaterie hohe Energiedichte aus.

Sind Dichte und Temperatur hoch genug, so sollte im Rahmen der Theorie der QCD¹ die chirale Symmetrie teilweise wieder hergestellt werden. Verschiedene theoretische Modelle sagen für den Fall der Wiederherstellung der chiralen Symmetrie signifikante Änderungen der Vektormesoneneigenschaften, insbesondere von  $\rho$  und  $\omega$ , voraus. HADES ist so konzipiert, daß es eine eventuelle Änderung der Mesonenmasse nachweisen kann.

In zentralen 1 AGeV Au + Au Kollisionen wird eine Produktionswahrscheinlichkeit für Dielektronen aus dem Massenbereich der  $\rho$ - und  $\omega$ - Vektormesonen von nur etwa 3 ·10<sup>-6</sup> erwartet ([Win93],[Wol93]). Um trotzdem zu ausreichender Statistik zu kommen, muß die Kollisionsrate 10<sup>8</sup> pro Sekunde betragen denn nur etwa jede zehnte Kollision ist als zentral anzusehen (b < 3 fm), sodaß im gesamten Raumwinkel etwa 18 Dielektronen pro Minute zu erwarten sind. Um diese geringe Anzahl von Dielektronen aus dem bei jeder Au + Au Kollision entstehenden hadronischen Untergrund von 170 Protonen und 20 geladenen Pionen herauszufiltern, werden sehr effiziente Methoden zur Hadronendiskriminierung benötigt.

Durch die hohen Kollisionsraten und den hohen Untergrundanteil in den Daten werden sehr hohe Anforderungen an das Triggerkonzept gestellt. Selbst bei der Beschränkung auf zentrale Stöße gibt es noch alle 10  $\mu$ s ein Ereignis. Im Abschnitt 3.1 werden die erwarteten Datenraten der Driftkammern dargelegt. Die Ausleseelektronik im HADES - Systems ist daher so konzipiert, daß eine Auslese aller aktiven Kanäle in weniger als 10  $\mu$ s erreichbar wird. Dies führt zu einer primären Datenrate von etwa 3 Gigabyte pro Sekunde. Durch zwei zusätzliche Triggerstufen muß die Datenmenge weiter reduziert werden, indem nur Ereignisse mit vollständig identifizierten Leptonenspuren akzeptiert werden (siehe Abschnitt 2.2).

Um diese Anforderungen für die zur Spurverfolgung aller geladenen Teilchen eingesetzten Driftkammern zu realisieren, wurde eine mehrere Komponenten umfassende spezifische Ausleseelektronik entworfen. Im Rahmen dieser Arbeit wird dieses Auslesesystem vorgestellt (siehe Kapitel 3) und spezielle Aspekte, wie die Segmentierung der Komponenten zur Optimierung der Auslesegeschwindigkeit, diskutiert (siehe Kapitel 4.2). Der Schwerpunkt der Arbeit liegt im Aufbau eines Testsystems, mittels dessen der zur Digitalisierung der Driftzeitinformationen verwendete TDC getestet wurde. Dieser TDC ist als kundenspezifischer, integrierter CMOS-Baustein realisiert und wird detailliert in Kapitel 5 vorgestellt. Durch Testmessungen wurde überprüft, ob die Prototypversionen dieses ASICs² die Spezifikationen einhalten, alle Optionen funktionsfähig sind und die geforderte Auflösung erreicht wird. Die Ergebnisse dieser Testmessungen werden in Kapitel 6 zusammen mit dem Testaufbau vorgestellt.

Eine Bewertung der Testergebnisse, sowie ein Ausblick folgen in Kapitel 7.

<sup>&</sup>lt;sup>1</sup>Quanten Chromo Dynamik

<sup>&</sup>lt;sup>2</sup>ApplicationSpecific IntegratedCircuit

# Kapitel 2

# HADES, das zukünftige Dileptonenspektrometer an der GSI

# 2.1 Konzept der Dileptonen - Identifikation

Beim Zweikörperzerfall eines im Labor ruhenden Teilchens werden die Zerfallsprodukte unter 180° emittiert. Bewegt sich das zerfallende Teilchen jedoch, so erhalten die Zerfallsprodukte eine Geschwindigkeitskomponente in derselben Richtung wie die Bewegung des zerfallenden Teilchens. Es ist daher ausreichend, wenn das Detektorsystem so konzipiert ist, daß es im wesentlichen den Vorwärtswinkelbereich abdeckt. Der Akzeptanzbereich des Spektrometers erstreckt sich von 18° relativ zur Strahlachse bis hin zu 85°.

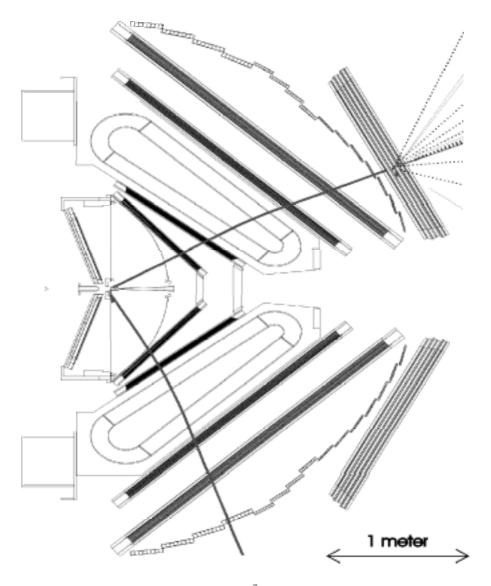

Der entscheidende Designaspekt des Spektrometers ist die Identifizierung von Elektronen und Positronen in einem Untergrund von Hadronen mit hoher Multiplizität. Damit dies bereits auf Triggerniveau erreicht werden kann, werden verschiedene Detektorsysteme benutzt. Um eine Unterscheidung zwischen  $e^+$  und  $e^-$  vornehmen zu können und insbesondere deren Impuls zu bestimmen, ist eine Spurverfolgung durch ein Magnetfeld nötig. Bei HADES werden hierfür ein toroidales Magnetfeld (vgl. 2.3.1) und vier Ebenen von Driftkammern eingesetzt. Da je zwei Ebenen von Spurkammern vor und hinter dem Magneten verwendet werden, kann die Spurinformation zuverlässiger mit den Signalen in RICH¹ und META² koordiniert werden. Abbildung 2.1 zeigt einen Schnitt durch das HADES Detektor System. Zum besseren Verständnis sind die Spuren eines Leptonenpaares gezeigt, die von dem System eindeutig identifiziert wurden.

<sup>&</sup>lt;sup>1</sup>Ring Imagigne Cherenkove Detektor

<sup>&</sup>lt;sup>2</sup>Multiplicity Electron Trigger Array

Im folgenden soll das Triggerkonzept vorgestellt werden, da es einen starken Einfluß auf die Auslegung der Ausleseelektronik hat. Danach wird die Funktionsweise der einzelnen Komponenten kurz diskutiert, wobei der Schwerpunkt auf der Datenauslese der Driftkammern gelegt ist.

Abbildung 2.1: Schnitt durch HADES. Dargestellt sind alle Detektoren und die Magnetspulen. Der Übersichtlichkeit halber ist die Tragkonstruktion weggelassen. Aus [Sch95]

# 2.2 Das HADES - Triggerkonzept

Aufgabe des HADES - Triggersystems ist die Identifikation von Ereignissen mit Dielektronen. Dazu muß es in der Lage sein, die Signale der Detektoren nach den seltenen Dielektronen zu durchsuchen.

Neben den seltenen Ereignissen, nach denen gesucht wird, gibt es generell in kernphysikalischen Experimenten immer auch Ereignisse, die keinen Beitrag zur untersuchten Physik liefern. Es ist die Hauptaufgabe des Triggers solche Ereignisse herauszufiltern. Während bei kleinen Experimenten in der Regel eine einfache Triggerlogik (Koinzidenz zwischen zwei Detektoren etc.) ausreicht, erfordern die Gegebenheiten bei HADES ein deutlich umfangreicheres Konzept.

Drei Triggerstufen sind nötig bis der Datenstrom nur noch die Ereignisse enthält, die zur Klärung der zu untersuchenden Physik bei HADES beitragen. Jede Triggerstufe bezieht neben den Informationen aus der vorangegangenen noch einen weiteren Detektor mit ein.

#### Erste Triggerstufe:

In dieser findet über die Untersuchung der Teilchenmultiplizität $^3$ eine Selektion auf zentrale Stöße statt. Wenn die Teilchenmultiplizität eine bestimmte Schwelle überschreitet, ist das Ereignis als zentral anzusehen. Durch diese Selektion wird die Ereignisrate um einen Faktor zehn reduziert. Als Detektoren zum Erfassen der Teilchenmultiplizität dienen der Schauerdetektor und  ${\rm TOF}^4$ , die beiden Komponenten des META-Systems.

#### Zweite Triggerstufe:

In einem ringabbildenden Cherenkov - Zähler erzeugen die mit hohem  $\gamma$  propagierenden Leptonen<sup>5</sup> Ringe, wobei der Detektor gegen Hadronen blind ist. Werden in einem Ereignis zwei solcher Ringe beobachtet, so müssen auch im

äußersten Detektorsystem META zwei Leptonenereignisse signalisiert werden. Im Winkelbereich oberhalb von 45° geschieht die Erkennung von Leptonen über die Flugzeit der Teilchen durch deren Nachweis in einem Szintillationszähler. Unterhalb dieses Winkels können hierdurch Leptonen nicht hinreichend gut gegen schnelle Pionen diskriminiert werden und der Nachweis erfolgt daher über die Ausbildung eines charakteristischen elektromagnetischen Schauers in

$<sup>^3</sup>$ Die folgenden Überlegungen gelten für einen Au + Au Stoß. Bei hadroneninduzierten Reaktionen ( $\pi$ -Strahl) werden selektive Reaktionstrigger verwendet.

<sup>&</sup>lt;sup>4</sup>Time of Flight

<sup>&</sup>lt;sup>5</sup>Im folgenden wird der Begriff Leptonen verwendet, um in Einschränkung seiner Bedeutung Elektronen und Positronen zu bezeichnen.

einem speziell hierfür entwickelten Detektor. Dadurch wird eine Reduktion der Ereignissrate um einen Faktor 100 erreicht.

#### **Dritte Triggerstufe:**

Zum Schluß werden auch noch die Daten der Driftkammern (siehe Abschnitt 2.4) in die Triggerentscheidung mit einbezogen. Aus diesen läßt sich eine Aussage über Impuls, Ladung und Entstehungsort des Teilchens erhalten. In dieser dritten Triggerstufe wird nach Korrelationen aus Treffern in den Driftkammern mit Ereignissen im Schauerdetektor und Ringen im RICH - Detektor gesucht. Dadurch werden zufällige Koinzidenzen gegenüber tatsächlichen Korrelationen unterdrückt. Diese Triggerstufe liefert nochmals eine Reduktion der Triggerrate um einen Faktor 10.

Damit die Triggerlogik genug Zeit hat, die Daten zu bearbeiten, müssen diese zwischengespeichert werden. Dies geschieht in sogenannten Pipes. Diese können entwerder mit normalen RAM <sup>6</sup> Speicherbausteine oder mit FIFO's<sup>7</sup> realisiert werden. Im Rahmen des HADES Triggerkonzeptes werden zwei Pipes benötigt. Die erste speichert die Daten nach der ersten Triggerentscheidung. Die Größe dieser Pipe muß so gewählt werden, daß sie alle Ereignisse aufnehmen kann, die eintreffen bis die zweite Triggerstufe ihre Entscheidung getroffen hat.

Die zweite Pipe speichert die Ereignisse, die von der zweiten Triggerstufe als gültig erkannt wurden. Die Größe der Pipe wird durch die Anzahl der Ereignisse, die bis zur dritten Triggerentscheidung eintreffen, bestimmt.

Die Verteilung der Triggersignale geschieht über den HADES - Triggerbus [Kas96]. An diesen sind die zentrale Triggereinheit (CTU<sup>8</sup>), die alle Triggerentscheidungen der verschiedenen Verarbeitungsstufen entgegennimmt, und die Detektortriggereinheiten (DTU<sup>9</sup>) angeschlossen. Die Detektortriggereinheit empfängt von der zentralen Triggereinheit die Triggersignale über den Triggerbus. Damit ist sichergestellt, daß alle Detektorsysteme die Triggersignale zur gleiche Zeit empfangen. Die einzelnen Detektortriggereinheiten signalisieren über die "Busy" ("beschäftigt") - Leitung der zentralen Triggereinheit, ob sie bereit sind, weitere Trigger entgegenzunehmen. Über den Detektortriggerbus leitet die Detektortriggereinheit die Triggerinformationen weiter an die einzelnen Module der Detektorelektronik.

<sup>&</sup>lt;sup>6</sup>Random Access Memory

<sup>&</sup>lt;sup>7</sup>FIFO = First In, First Out; Speicher, der nicht frei addressiert werden kann, sondern bei lesendem Zugriff immer das am längsten gespeicherte Datum liefert.

<sup>&</sup>lt;sup>8</sup>Central Trigger Unit

<sup>&</sup>lt;sup>9</sup>**D**etector **T**rigger **U**nit

# 2.3 Aufbau des Spektrometers

## 2.3.1 Magnet

Das erforderliche toroidale Magnetfeld wird durch sechs supraleitende Feldspulen erzeugt. Zwei dieser Spulen sind in Abbildung 2.1 zusammen mit den Umrissen der Spulenkästen eingezeichnet. Jede dieser Spulen besteht aus zwei geraden Teilstücken, deren Verbindung über Kreisbögen hergestellt wird. Die Feldspulen bilden die Grenzen zwischen den sechs Segmenten des HADES - Systems. Da sie die azimutale Akzeptanz des Spektrometers einschränken, muß ihre Dicke so gering wie möglich gehalten werden. Ihre Breite definiert den Raum, der zum Unterbringen von Elektronik und Kabeln zur Verfügung steht (vgl. Kapitel 4.2). Der Magnet muß hauptsächlich zwei Rahmenbedingungen erfüllen. Zum einen muß der Bereich, in dem sich der RICH befindet, nahezu feldfrei gehalten werden. Zum anderen muß die transversale Ablenkung der Teilchen stark genug sein, um ihren Impuls mit ausreichender Genauigkeit auflösen zu können ( $\delta p/p = 1\%$  - 1.5%). Dazu ist eine maximale Feldstärke von 0,5 T nötig.

Beide Bedingungen werden von einem toroidalen Magnetfeld, das von supraleitenden Feldspulen erzeugt wird, erfüllt. Durch den Einsatz von Supraleitern (Zusammensetzung AlCu:NbTi = 10:1 und Al:Cu(NbTi) = 3:1) für die Magnetspulen reduziert sich die effektive Dichte  $x/X_0$  für geladene Teilchen, da die Spulen sehr kompakt gebaut werden können. Bei einer mittleren Stromdichte von 100 - 120 A/mm² beträgt die im Feld gespeicherte Energie etwa 1,4 MJ bei einem totalen Strom durch die Spulen von 4,85·10<sup>5</sup> A·N (N = Windungszahl). Um diese Energie im Falle eines Feldzusammenbruchs abführen zu können, ist dem Spulenmaterial der hohe Anteil an Normalleitern zugesetzt. Es wird dabei mehr Al verwendet, da dessen Strahlungslänge um einen Faktor sechs höher ist als die von Cu, und dadurch weniger zum Untergrund beiträgt.

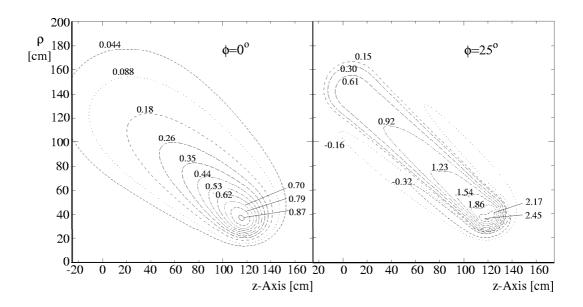

Abbildung 2.2 zeigt den Feldverlauf, der durch die HADES Magnetspulen erzeugt wird als Ergebnis einer Simulation. Nach Aufbau der Spulen wird das Feld detailliert vermessen, da die Information über den Feldverlauf zur Kalibrierung der Daten benötigt wird.

Abbildung 2.2: Simulierte Feldverteilung im HADES-Toroid in der Ebene der Koordinaten z und  $\rho$ , die entlang (z) senkrecht ( $\rho$ ) zur Spektrometerachse definiert sind.

**Links**: Mitte eines Segments ( $\Theta = 0^{\circ}$ ). Rechts: In Spulennähe ( $\Theta = 25^{\circ}$ ). Die Spule befindet sich bei  $\Theta = 30^{\circ}$ . Die Feldstärke ist in Tesla angegeben. Aus [Sch95]

# 2.3.2 Ringabbildender Cherenkov - Detektor (RICH)

In einem ortsempfindlichen Cherenkov - Detektor mit  $C_4F_{10}$  als Radiatorgas, in dem nur Leptonen Cherenkov - Licht<sup>10</sup> aussenden, können diese bei einem Untergrund von 170 Protonen und 20 geladenen Pionen identifiziert werden. Über einen sphärischen Spiegel wird das entstandene Cherenkov - Licht in den Photonen - Detektor reflektiert. Als Photokathode wird CsI verwendet. Zum Trennen von Radiator- und Zählgas dient ein  $CaF_2$  Fenster, das auch als Photonenkonverter dient. Die Ortsempfindlichkeit des Photonendetektors beruht auf der Pad - Struktur der Photokathode. Diese erlaubt eine theoretische Winkelauflösung von 2,3 mrad sowohl in azimutaler als auch in polarer Richtung unter Vernachlässigung der Einflüsse der Vielfachstreuung [Sch95].

Durch die Abbildungseigenschaften des Spiegels werden die Photonen des Cherenkov - Kegels als Ringe auf die Photokathode abgebildet. Durch Leptonenpaare mit kleinen Öffnungswinkeln, die vorzugsweise bei der externen Paarerzeugung und beim Dalitz - Zerfall des  $\pi^0$  Mesons auftreten, entstehen Doppelringe. Die Ausleseelektronik sucht in den Daten nach Ringmustern. Dabei werden die Doppelringe gesondert behandelt.

<sup>&</sup>lt;sup>10</sup>Cherenkov - Licht entsteht beim Durchflug eines Teilchens durch Materie, wenn die kinetische Energie des Teilchens größer ist als die Lichtgeschwindigkeit in der Materie.

## 2.3.3 Flugzeit - Wand (TOF)

Zur Messung der Flugzeit der Dielektronen werden organische Szintillatormaterialien eingesetzt. Ein Detektorsegment besteht aus parallelen Szintillatorstäben, deren Querschnitt mit zunehmendem polarem Winkel in Anpassung an die abnehmende Multiplizität größer wird. Sie werden an beiden Enden durch Sekundärelektronenvervielfacher ausgelesen. Die Ortsauflösung in polarer Richtung wird durch die Segmentierung der Szintillatoren erreicht. Die Laufzeitunterschiede der Signale zu den beiden Enden der Szintillatoren liefern eine Information über die azimutale Position des durchgeflogenen Teilchens.

## 2.3.4 Multiplizitätsdetektor (Shower)

Der Schauerdetektor besteht aus drei Drahtkammern mit je einer Ebene von Signaldrähten. Zwischen diesen Drahtkammern befindet sich je eine Bleiplatte von 12 mm Dicke, die als Konverter dient. Ein Lepton löst beim Durchflug durch diesen einen elektromagnetischen Schauer von Sekundärelektronen aus, die in der nachfolgenden Drahtkammer eine größere Anzahl von Signaldrähten aktivieren. Durch Berechnung des Ladungsschwerpunktes eines Schauers kann man den Ort des Durchflugs des Teilchens bestimmen. Hadronen hingegen erzeugen durch starke Wechselwirkung nur Schauer mit vergleichsweise geringer Multiplizität. Durch Begutachtung der Schauercharakteristik können so Leptonen von Hadronen unterschieden werden. Die Dicke des Konverters ist so gewählt, daß Teilchen von wenigen 100 MeV einen Schauer mit ausreichender Statistik bilden.

# 2.4 Die Vieldraht - Driftkammern

# 2.4.1 Aufgabe

Aufgabe der Driftkammern ist die Verfolgung der Spuren aller geladenen Teilchen. Da jeweils zwei Positionsbestimmungen vor und hinter dem Magnetfeld stattfinden, läßt sich die Ablenkung eines Teilchens einfach berechnen zu:

$$B \cdot \rho = \frac{p}{q} \tag{2.1}$$

mit B = Fluß,  $\rho$  = Radius der Krümmung, p = Impuls und q = Ladung. Aus der Ablenkung ergibt sich bei bekannter Ladung der Impuls. Um die Massenauflösung von kleiner als 1% zu erreichen muß die Genauigkeit der Positionsbestimmung im Bereich von 100  $\mu$ m liegen [Sch95].

Weiterhin werden beim Bau der Driftkammern soweit als möglich Materialien mit kleiner Ordnungszahl verwendet. Dadurch wird verhindert, daß die Trajektorie durch Vielfachstreuung modifiziert wird und damit die Impulsbestimmung leidet.

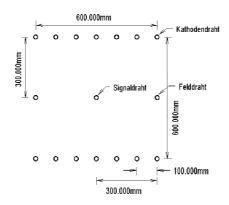

Abbildung 2.3: Aufbau einer Driftzelle.

Um auch bei Vielfachstreuung in einer Kammer die eindeutige Rekonstruktion der Durchtrittsorte zu ermöglichen, werden pro Kammer insgesamt sechs Ebenen von Driftzellen verwendet und die Größe der Zellen so gewählt, daß Doppeltreffer in einer Zelle eine Wahrscheinlichkeit von 35 % haben.

#### 2.4.2 Aufbau

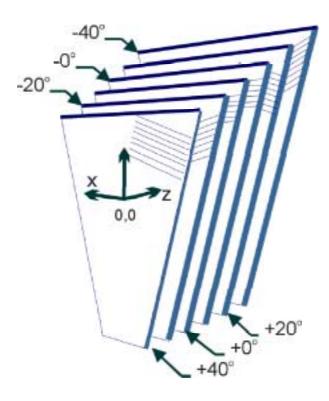

Den Aufbau einer Driftzelle zeigt Abbildung 2.3. Jede Driftzelle besteht aus dem Signaldraht, den beiden parallel dazu verlaufenden Felddrähten im Abstand einer halben Zellgröße und den beiden Ebenen von Kathodendrähten. Die HADES - Driftkammern besitzen sechs Ebenen Driftzellen. Die Signaldrähte sind unter fünf verschiedenen Winkeln angeordnet (Abbildung 2.4), sodaß die Ortsauflösung in Richtung der Ablenkung etwa einen Faktor 2 genauer ist als in azimutaler Richtung. Die Größe der Driftzellen nimmt von Ebene I bis Ebene IV zu um die Granularität in allen Ebenen konstant zu halten. Bei Ebene I beträgt sie 5 mm, bei Ebene IV 14 mm. Die Drahtabstände sind entsprechend der nach außen abnehmenden Teilchenbelegungsdicht so gewählt, daß die Doppeltrefferwahrscheinlichkeit für eine Zelle 35 % beträgt. Das aktive Volumen der Driftkammer bilden abwechselnde Lagen von Kathoden- und Signalebenen. Während in den Kathodenebenen die 80  $\mu$ m dicken Aluminiumdrähte immer in y-Richtung verlaufen, bestehen die Leseebenen aus einer alternierenden Folge von Felddrähten (ebenfalls 80  $\mu$ m Aluminium) sowie 80  $\mu$ m dicken Signaldrähten aus Wolfram.

Das Gasvolumen der Kammer wird auf beiden Seiten von einer aluminisierten Kaptonfolie von 12  $\mu$ m Dicke begrenzt. Als Zählgas wird eine Mischung von 70 % Helium mit 30 % Isobuthan verwendet.

Durch die unterschiedliche Geometrie der einzelnen Ebenen enthält jede eine unterschiedliche Anzahl an Signaldrähten. Diese sind in Tabelle 2.1 zusammengefaßt.

Abbildung 2.4: Aufbau der Driftkammern am Beispiel eines Moduls. Dargestellt ist die Anordnung der Zellebenen mit ihrer unterschiedlichen Orientierung der Drähte. Die Lage der Drähte ist nur angedeutet. Die z-Achse zeigt in Richtung der Teilchenflugbahn, die y-Achse in Richtung der prinzipiellen Ablenkung der Teilchen im Magnetfeld. Aus [Str97a]

#### 2.4.3 Funktionsweise

Die Funktionsweise von Driftkammern entspricht im wesentlichen der von Proportionalzählrohren. Ein geladenes Teilchen erzeugt bei seinem Durchflug durch das Gasvolumen der Kammer durch Ionisation von Gasmolekülen freie Elektronen. Diese driften entlang der Feldlinen mit gleichbleibender Geschwindigkeit zum Anodendraht (Signaldraht) hin. Da aufgrund des kleinen Durchmessers des

| Anzahl der Signaldrähte |     |     |      |      |      |      |       |

|-------------------------|-----|-----|------|------|------|------|-------|

|                         | +0° | -0° | +20° | -20° | +40° | -40° | Total |

| Modul 1                 | 163 | 163 | 184  | 184  | 184  | 184  | 1062  |

| Modul 2                 | 166 | 164 | 185  | 185  | 184  | 184  | 1068  |

Tabelle 2.1: Anzahl der Signaldrähte pro Ebene für die Driftkammermodule I+II

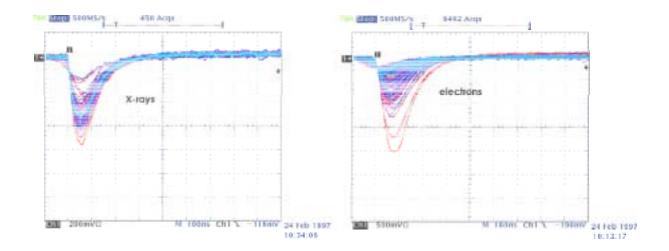

Abbildung 2.5: Signal der Prototyp - 1 - Driftkammer. Das linke Teilbild zeigt das Signal einer Eisen - 55 - Quelle, das rechte Bild das einer Strontium - 90 - Quelle. Aufgenommen wurde das Signal, indem auf die fallende Flanke getriggert wurde.

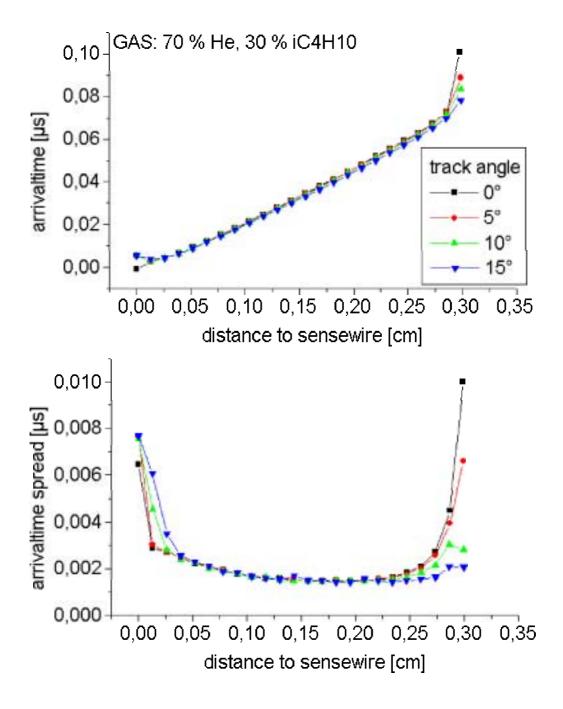

Signaldrahtes das Feld an der Oberfläche stark ansteigt, kommt es in seiner Nähe zu Gasverstärkung. Dabei werden die Elektronen so stark beschleunigt, daß weitere Gasmoleküle von den Elektronen durch Stoßprozesse ionisiert werden. Hierbei werden etwa 10<sup>5</sup> mal soviele freie Ladungsträger erzeugt, deren Driftbewegung dem Feld soviel Energie entzieht, daß im Vorverstärker ein meßbares Spannungssignal erzeugt wird. Abbildung 2.5 zeigt zwei Beispielsignale, wie sie von der Kammer geliefert werden. Um die in Abbildung 2.6 als Ergebnis einer GARFIELD<sup>11</sup> Simulation wiedergegebene Ankunftszeit der Primärladungen zu messen, benötigt man als Trigger den Zeitpunkt des Durchfluges des Teilchens durch die Zelle. Dieser wird aus einem speziellen Startzähler abgeleitet. Dabei kommt es auf ein stabiles Zeitverhalten dieses Signales an, da ansonsten die Messung der Driftzeit mit Fehlern behaftet ist.

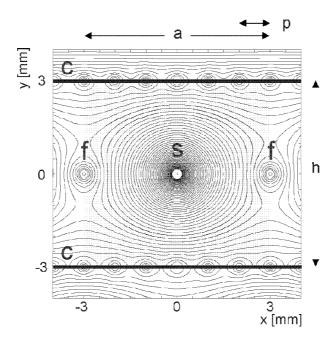

Es zeigt sich, daß die Ankunftszeit der ersten Elektronen von der Durchflugsrichtung nahezu unabhängig ist. Abbildung 2.6 verdeutlicht dies. Es sind die Ankunftszeiten für vier verschiedene Winkel aufgetragen gegen die Entfernung vom Signaldraht. Wie die Abbildung zeigt, wächst die Ankunftszeit über einen weiten Entfernungsbereich zwischen Signal- und Felddraht linear. Lediglich in unmittelbarer Nähe von Signal und Felddraht liegt die Ankunftszeit über der anhand des linearen Verlauf erwarteten Zeit. Grund für diese Abweichung ist der Verlauf der Driftlinien. Diese sind durch die Geometrie des Feldes in der Driftzelle gegeben. Abbildung 2.7 zeigt die Äquipotentiallinien in einer Driftzelle.

Für Teilchen, die in der Nähe von Signal- bzw. Felddraht durch die Driftzelle

$<sup>^{11}\</sup>mathrm{Programm}$  zur zweidimensionalen Simulation von Driftkammern. Teil der CERN Programmlibrary

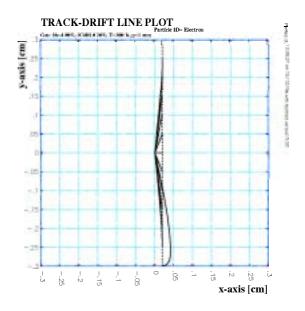

fliegen, sind die Längen der Driftwege unterschiedlich, je nachdem an welchem Ort die Elektronen entstehen. Als Beispiel zeigt Abbildung 2.8 die Driftwege von Elektronen für eine Teilchenspur in der Nähe eines Signaldrahtes. Für Teilchen, deren Flugbahn um weniger als ≈15° von der Senkrechten auf die Signaldrahtebene abweicht, kann angenommen werden, daß die Elektronen, die entlang einer Verbindungslinie zwischen Signal- und Felddraht gebildet werden, als erste am Signaldraht eintreffen. Für Teilchen, die unter einem größeren Winkel durch die Driftzelle fliegen, liefert die Driftzeit nur eine Angabe über eine radiale Entfernung vom Signaldraht. Durch Hinzuziehen von Informationen aus einer weiteren Driftzellebene kann ermittelt werden, unter welchem Winkel zur Signaldrahtebene das Teilchen durch die Zelle geflogen ist. In [Zen97] wurde gezeigt, daß über einen weiten Bereich der Driftzelle ein linearer Zusammenhang zwischen Ankunftszeit und Entfernung der Teilchenspur vom Signaldraht besteht. Da die Ionisation statistisch verteilt über die Spur auftritt, ergibt sich eine Variation in der Ankunftszeit für Teilchen mit gleicher Entfernung zum Signaldraht. Dies hat Einfluß auf die Ortsauflösung der Driftkammer.

In [Zen97] ist eine detaillierte Untersuchung der Ankunftszeit der Elektronen durchgeführt worden. [Wal93] gibt eine umfassende Darstellung der Driftkammerphysik. Informationen über den Betrieb von Driftkammern findet man auch in [Sau77].

## 2.4.4 Bestimmung der Driftgeschwindigkeit

Zur Bestimmung der Driftgeschwindigkeit benötigt man externe Referenzdetektoren. Dafür eignen sich zum Beispiel Silizium - Mikrostreifen - Detektoren (MSD). Bestimmt man mit diesen Detektoren jeweils vor und hinter der Driftkammer den Ort eines Teilchens, so kann man die Orte in den Referenzdetektoren miteinander korrelieren und erhält dadurch Trajektorien durch die Driftkammer. Durch Messen der Zeit, die zwischen dem Durchflug des Teilchens und dem Eintreffen der Elektronen am Signaldraht vergeht, kann man die Driftgeschwindigkeit bestimmen. Diese ist stark von der Zusammensetzung des Detektorgases abhängig. Sie ist für das in den HADES-Kammern verwendete Zählgas He-i-Buthan (70/30) in einem weiten Feldstärkebereich des Detektors konstant und beträgt 4 cm/ $\mu$ s. Der Nachweis findet sich in [Zen97]. Eine ausführliche Beschreibung der Methode zur Bestimmung der Driftgeschwindigkeit gibt [Ste97].

#### 2.4.5 Entstehung der Trackinginformation

Eine grobe Ortsinformation erhält man, indem man die Raumpunkte ermittelt, an denen sich die getroffenen Drähte kreuzen. Es müssen mindestens von drei Ebenen Informationen zur Verfügung stehen, da die Information einer einzelnen Zelle keine Aussage erlaubt, auf welcher Seite des Signaldrahtes das Teilchen durch die Zelle geflogen ist(vgl. [Sch95]). Zur Erhöhung der Ortsauflösung zieht man die Information über die Driftzeit heran.

Mit Kenntnis der Driftgeschwindigkeit kann man aus der Driftzeit den kürzesten Abstand vom Draht bestimmen, bei dem das Teilchen durchgeflogen ist.

$$x = v_D * (t_{arrival} - t_{offset}) \tag{2.2}$$

Dabei ist x die Entfernung des Teilchens vom Meßdraht,  $v_D$  die Driftgeschwindigkeit und  $t_{arrival}$  die gemessene Driftzeit und  $t_{offset}$  die durch Signallaufzeiten in Kabeln und der Elektronik verursachte Verzögerung.

Abbildung 2.6: Ankunftszeitverteilung für das Gasgemisch mit 70% Heliumanteil als Ergebnis einer GARFIELD Simulation. Dargestellt ist die Ankunftszeitverteilung für vier verschiedene Winkel der Teilchenspur. Der untere Teil der Abbildung zeigt die theoretisch erwartete Auflösung der Ankunftszeit. Aus [Zen97].

Abbildung 2.7: Feldverlauf einer Driftzelle der Driftkammerebene II. Es bedeuten : C Kathodendrähte, F Felddraht und S Signaldraht. Die Abmessungen sind a=6 mm, h=6 mm und p=1 mm.

Abbildung 2.8: Durchgang eines Teilchens durch die Driftkammer in der Nähe des Signaldrahtes. Eingezeichnet sind die Driftwege einiger Elektronen entlang dieser Spur. Aus [Zen97] Seite 37.

# Kapitel 3

# Auslesekonzept der Driftkammern

#### 3.1 Die Datenraten

Für das Verständnis des Auslesesystems ist es hilfreich, die erwarteten Datenraten zu kennen. Das Datenerfassungskonzept von HADES sieht 3 Triggerstufen vor, die wie bereits in Kapitel 1 erwähnt, unterschiedliche physikalische Bedingungen stellen. Dadurch, daß die Bedingungen von Stufe zu Stufe immer enger gefaßt sind, führen sie natürlich zu einer Reduktion der Datenmenge. Im folgenden sollen die erwarteten Datenraten in Bezug auf die Driftkammern erläutert werden. Die physikalische Bedeutung der einzelnen Trigger ist in Kapitel 2.2 erläutert.

#### Ereignisraten

Die Ereignisrate wird von den physikalischen Verhältnissen des verwendeten Stoßsystems bestimmt. Für Au + Au - Kollisionen ergibt eine Strahlintensität von  $10^8$  Projektilionen/s auf ein Target von 1% nuklearer Wechselwirkungslänge eine Kollisionsrate von  $10^6/\mathrm{s}$ .

#### Erste Triggerstufe

Durch den Trigger der ersten Stufe werden alle zentralen Stöße akzeptiert. Dadurch erhält man eine Ereignisrate von  $10^5/\mathrm{s}$ . Simulationen [Sch95] haben ergeben, daß ungefähr 20 Teilchen durch jeden Sektor fliegen werden. Grundlage dieser Simulationen ist ein relativistisches Modell. Mit diesem wurden Au + Au Kollisionen bei 1 AGev simuliert. Es gibt, auf alle sechs Sektoren verteilt, 24 Driftkammermodule mit je sechs Drahtebenen. Somit erhält man  $2,88 \cdot 10^8$  Signale/s.

Um die Überlagerung von zwei Teilchen, die durch dieselbe Driftzelle fliegen, auflösen zu können, triggert jedes Analogsignal den TDC¹ sowohl mit der steigenden als auch der fallenden Flanke. Damit ergibt sich eine Datenrate von  $5,76 \cdot 10^8/\mathrm{s}$ . Von den 14 Bit der TDC - Zeitdaten werden nur 11 Bit verwendet. Hinzu kommen noch 8 Bit der TDC - Adresse wodurch man eine Datenmenge von  $1,094 \cdot 10^{10}$  Bits/s erhält. Das entspricht 1,27 Gigabyte pro Sekunde.

#### Zweite Triggerstufe

Durch die zweite Triggerstufe findet eine Reduktion der Ereignisrate um ca. einen Faktor 100 statt. Nach der im vorhergehenden Abschnitt beschriebenen Rechnung ergibt sich damit eine Datenmenge von 13,04 MB/s.

#### **Dritte Triggerstufe**

Der Trigger der dritten Stufe nimmt noch einmal eine Reduktion um einen Faktor 10 vor. Somit bleiben nun nur noch  $10^2$  Ereignisse pro Sekunde, die als physikalisch relevant erachtet und auf Band geschrieben werden. Unter denselben Annahmen erhält man nun noch eine Datenmenge von 1,3 MB/s.

# 3.2 Das Konzept

Im Rahmen dieser Arbeit wurde ein Konzept zur Auslese der Vieldraht - Driftkammern entwickelt. Aufgabe des Systems ist die Digitalisierung der Driftzeiten von ca. 27.000 Driftzellen mit einer Rate von  $10^5/\mathrm{s}$ . Im folgenden soll anhand von Abbildung 3.1 das Auslesekonzept erläutert werden.

Das Triggerkonzept sieht vor, daß die Daten an zwei Stellen im Verlauf der Auslese zwischengespeichert werden. Dadurch entstehen drei unterschiedlich weit reduzierte Datentypen. Die Daten, die durch ein Signal der ersten Triggerstufe digitalisiert werden, bezeichnet das Konzept als LVL1 Daten(Level-1 Data). Die Digitalisierung wird von den TDC auf den Motherboards durchgeführt. Unmittelbar nach Abschluß der Digitalisierung werden die Daten aus den TDC's ausgelesen, und zu den Auslesesteuereinheiten übertragen. Diese werden in der Abbildung mit "read-out controller" bezeichnet. Auf diesen werden sie in einem Speicher abgelegt bis die zweite Triggerstufe entschieden hat, ob die Daten ein Dileptonenereignis darstellen. Die Prozessoren der zweiten Triggerstufe benötigen 100 - 150  $\mu$ s [Kü], um eine Entscheidung zu treffen. Auf den Auslesesteuerungseinheiten muß im Speicher Platz sein, um alle während dieser Zeit eintreffenden Ereignisse puffern zu können. Der Speicher auf den Auslesesteuerungseinheiten soll 30 Kiloworte speichern können. Dies reicht aus, um selbst bei zentralen Au + Au Stößen 64 Ereignisse speichern zu können. Die Anzahl der Motherboards wird durch die Anzahl der Signaldrähte einer

$<sup>^{1}</sup>$ Time to Digital Converter = Zeit zu Digital Wandler

Abbildung 3.1: Prinzip der Auslese der Driftkammern. Dargestellt ist, wie die einzelne Komponenten zusammenwirken. Aus [Str97b].

Driftkammer bestimmt. Für die ersten beiden Ebenen werden je 14 Motherboards benötigt. Nutzt man aus, daß es möglich ist, mehrere Motherboards über eine Auslesesteuerungseinheit zu lesen, wie in Kapitel 4 erläutert, so benötigt man pro Driftkammermodul zehn Auslesesteuerungseinheiten.

Bei Eintreffen des Triggersignals der zweiten Triggerstufe werden die Daten von den Auslesesteuerungseinheiten zu den Konzentratoren übertragen. Dabei werden nur solche Ereignisse übertragen, die zu einem positiven Triggersignal geführt haben. Diese Daten sind in Abbildung 3.1 als LVL2 Daten bezeichnet. Dabei werden jeweils die zu einem Driftkammermodul gehörenden zehn Auslesesteuerungseinheiten von einem Konzentrator ausgelesen. Es werden somit 12 Konzentratoren benötigt, die zusammen in einem VME Überrahmen in der Meßhütte untergebracht sind. Auf den Konzentratoren werden die Ereignisse der einzelnen Auslesesteuerungseinheiten zusammengestellt und gespeichert, bis durch ein Triggersignal der dritten Triggerstufe entschieden wurde, ob sie verworfen, oder zur späteren Analyse abgespeichert werden.

Um die Entfernung zwischen Auslesesteuerungseinheiten, die in Überrahmen im Tragrahmen des Detektorsystems aufgehängt sind, und den Konzentratoren in der Meßhütte zu überbrücken, sind Leistungstreiber nötig. Diese befinden sich auf der in Abbildung 3.1 als DMA<sup>2</sup> Einheit bezeichneten Karte. Diese Karte erlaubt auch den Zugriff auf den Speicher der Auslesesteuerungseinheit, um die von den TDC benötigten Initialisierungsinformationen dort ablegen zu können.

Die Steuerung der Auslese nimmt die Detektortriggereinheit (DTU) vor. Sie ist über den HADES-Triggerbus mit der zentralen Triggereinheit (CTU) verbunden. Von dieser erhält sie die Triggersignale zusammen mit der Ereignisnummer des nächsten Ereignisses. Die Ereignisnummer wird zusammen mit dem Triggersignal über die Detektortriggerempfänger (DTR) zu den Auslesesteuerungseinheiten übertragen. Zur Adressierung des Speichers werden auf den Auslesesteuerungseinheiten die unteren sieben Bit der Ereignisnummer verwendet. Diese werden um soviele Bits nach links verschoben, daß der bei der Inkrementierung entstehende Speicherblock groß genug ist, die gesamten Daten aufzunehmen. Die Größe des Datenblockes muß mindestens 386 Datenworte betragen. Für den Fall, daß zwei Motherboards mit ie 12 TDC - Chips an die Auslesesteuerungseinheit angeschlossen sind, und alle acht TDC - Kanäle Daten liefern, werden 384 (= 24.8)Datenworte benötigt. Hinzu kommen noch das Datenwort mit der Ereignisnummer und die Information über die Anzahl der tatsächlich gelesenen Datenworte. Die Detektortriggereinheit verwaltet auch den Speicher auf den Auslesesteuerungseinheiten und den Konzentratoren. Durch Mitzählen der Signale der drei Triggerstufen kann sie durch Bilden der Differenz zwischen den einzelnen Zählern ermitteln, ob in den entsprechenden Speichern noch Platz ist. Sollte dies

<sup>&</sup>lt;sup>2</sup>DMA = **D**irect **M**emory **A**ccess; Direkter Speicherzugriff

| Verstärkung    | $10$ - $20~{ m mV}/\mu{ m A}$ |

|----------------|-------------------------------|

| Rauschen       | $< 1\mu A$                    |

| Anstiegszeit   | 10 ns                         |

| Abklingzeit    | < 50 ns                       |

| Übersprechen   | ≤ 1%                          |

| Stromverbrauch | $\leq 20 \text{ mV/Kanal}$    |

Tabelle 3.1: Parameter der Analogkarten. Aus [Str97b].

nicht der Fall sein, so signalisiert die Detektortriggereinheit diesen Zustand als "Pipe full"<sup>3</sup> an die zentrale Triggereinheit. Für den Speicher auf den Auslesesteuerungseinheiten zählt die Detektortriggereinheit die Triggersignale von erster und zweiter Triggerstufe, egal ob das Signal der zweiten Triggerstufe positiv oder negativ ist. Nur die positiven Triggersignale der zweiten Triggerstufe werden zur Entscheidung über den Speicher der Konzentratoren herangezogen.

# 3.3 Die Komponenten

## 3.3.1 Analogkarten (Daughterboards)

Mit den Analogkarten wird eine Aufbereitung des Kammersignals vorgenommen. Durch einen Verstärker wird zunächst das von der Kammer kommende Stromsignal in ein Spannunssignalg umgewandelt. Anschließend wird das Signal von einem Shaper<sup>4</sup> durch Integration des Signals geglättet. Wie in Kapitel 2.4.3 gezeigt, ist die Ankunftszeit der ersten Elektronen am Signaldraht proportional zum Abstand der Teilchenspur. Der Signalformer darf also die Flanke des Pulses nicht zeitlich verändern, damit die Ortsauflösung der Driftkammer nicht verschenkt wird. Zwischen Anstiegszeit und Signalverlauf muß daher ein Kompromiß gefunden werden. Der auf den Signalformer folgende Thresholddiskriminator vergleicht die Pulshöhe mit einer einstellbaren Schwelle. Übersteigt die Signalspannung die Schwelle, so wird der Ausgang des Diskriminators aufgesteuert. Durch Verstellen der Schwellenspannung können das Eigenrauschen des Verstärkers und Störungen am Eingang der Karte vom Ausgang ferngehalten werden. Die Spezifikationen der Analogkarten faßt Tabelle 3.1 zusammen.

Die Analogkarten werden zusammen mit den im folgenden Abschnitt beschriebenen Motherboards direkt am Detektor angebracht. Auf den Anschluß der Daughterboards an die Signaldrähte wird in Kapitel 4.2 eingegangen.

Jede Karte enthält 8 Kanäle Verstärker, Signalformer und Grenzwertschalter in

<sup>&</sup>lt;sup>3</sup>Ein in der HADES Datenauslese standardisiertes Signal an die zentrale Triggereinheit, das dazu führt, daß keine weiteren Triggersignale der ersten Triggerstufe generiert werden.

<sup>&</sup>lt;sup>4</sup>Shaper = Signalformer

einer integrierten Schaltung. Eingesetzt wird ein als ASD8 $^5$  bezeichneter Chip, der an der Universität von Pennsylvania (USA) entwickelt wurde. Da der Chip nur wenig externe Beschaltung benötigt, wurde die Größe der Analogkarten auf 90  $^*$  25 mm begrenzt.

## 3.3.2 Digitalisierung (Motherboards)

Mit dem Ausgangssignal der Analogkarten wird der Meßvorgang in den *Time to Digital Convertern*(TDC) gestartet. Das Signal für den Stop der Zeitmessung wird über die Auslesesteuerungseinheit (siehe 3.3.3) dem TDC zugeführt. Die digitalisierten Zeitdaten werden in den TDC - Chips in Registern zwischengespeichert. Die Auslesesteuerungseinheiten initiieren die Auslese, die von den TDC - Schnittstellen selbständig durchgeführt wird.

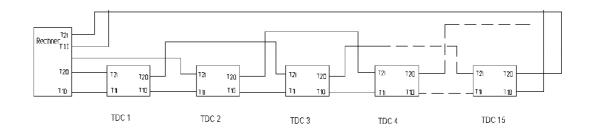

Die Rechnerschnittstelle des TDC (vgl. Abschnitt 5) erlaubt die Zusammenschaltung von bis zu 15 TDC's in einer Kette. Simulationen (siehe Kapitel 4) haben gezeigt, daß Karten mit 8 und 12 TDC - Chips benötigt werden. Zusätzlich ist vorgesehen, zwei Boards von einer Auslesesteuerungseinheit steuern zu lassen. Dazu werden die Karten über ihren Auslesebus in Reihe geschaltet. Die Logik der Karten sorgt dafür, daß immer nur eine angesprochen wird. Damit wird erreicht, daß die Datenrate pro Ereignis für einen einzelnen Auslesebus nicht die Bandbreite des Busses übersteigt. Auch die Motherboards werden direkt am Detektor angebracht. Sie sind über Platinenverbinder direkt mit den Daughterboards (siehe vorhergehenden Abschnitt) verbunden. In Kapitel 4 werden die Motherboards ausführlich beschrieben.

# 3.3.3 Auslesesteuerungseinheit (RC)

Die Auslesesteuerungseinheit (Readout - Controller (RC)) ist von der Elektronik her so einfach wie möglich gehalten. Auf ihr befindet sich Speicher zur Pufferung der Daten, ein FPGA<sup>6</sup> zur Steuerung der Auslese der TDC und die Schnittstellen zu Motherboard und DMA Einheit. Auf der Logik sind alle Funktionen zur Steuerung des TDC wie Auslese der Zeitdaten im Tokenmodus etc. implementiert. Als Speicher wird sogenanntes Dualported RAM<sup>7</sup> verwendet. Die Schnittstellen sind beide als differentielle Niederspannungsleitungen ausgeführt. Dadurch reduziert sich zum einen der Stromverbrauch und zum anderen wird die Übertragungssicherheit erhöht.

<sup>&</sup>lt;sup>5</sup>Amplifier Shaper Discriminator

$<sup>^6\</sup>mathrm{Field}$  Programable Gate Array - Feld programmierbares Gatter Netzwerk

<sup>&</sup>lt;sup>7</sup>Speicher mit zwei unabhängigen Adreßbussen

## 3.3.4 Konzentrator (SAM)

Die Konzentratoren (SAM<sup>8</sup>) behandeln die Entscheidungen der zweiten Triggerstufe. Wenn diese eine positive Entscheidung fällt, wird das zugehörige Ereignis aus allen angeschlossenen Auslesesteuerungseinheiten gelesen und im Speicher abgelegt. Die Konzentratoren sind als VME - Module ausgeführt. Das Protokoll auf dem Bus zwischen Auslesesteuerungseinheiten und Konzentrator ist dem des Bus zwischen TDC und Auslesesteuerungseinheit nachempfunden. Es werden mehrere Auslesesteuerungseinheiten von einem Konzentrator ausgelesen. Dabei überträgt er die Ereignisnummer des zu liefernden Ereignisses an die Auslesesteuerungseinheit. Diese liefern nun bei Eintreffen des Tokensignals, die Daten aus dem zugehörigen Speicherblock. Die Daten werden im Speicher des Konzentrators abgelegt, von wo sie die CPU mittels direktem Zugriff abholen kann, wenn das Ereignis von der dritten Triggerstufe akzeptiert wurde. Da die Entscheidung der dritten Triggerstufe unter Zuhilfenahme dieser Daten geschieht, müssen sie nicht nur im Speicher des Konzentrators abgelegt, sondern auch an den Prozessor der dritten Triggerstufe geliefert werden.

## 3.3.5 Bustreiberkarte (DTR + DMA)

Die logischen Funktionen von Detektortriggerempfänger (DTR) und Speicherzugriffseinheit (DMA), die in Abbildung 3.1 als getrennte Karten dargestellt sind, werden auf der Bustreiberkarte zusammengefaßt. Um auf den Auslesesteuerungseinheiten Platz zu sparen, werden die erforderlichen Treiber auf eine eigene Karte ausgelagert. Auf dieser sind die Treiber für den Datenbus zwischen Auslesesteuerungseinheiten und Konzentrator untergebracht. Daneben befindet sich auf der Karte noch der Treiber für den Detektortriggerbus, über den unter anderem die Ereignisnummern übermittelt werden. Wegen des kritischen Zeitverhaltens wird das Stopsignal für die TDC getrennt von diesen Bussystemen über eine schnelle Signalleitung geführt.

# 3.3.6 Detektortriggereinheit (DTU)

Die Detektortriggereinheit besitzt zwei Bussysteme. Zum einen den HADES - Triggerbus [Kas96], über den sie mit der zentralen Triggereinheit verbunden ist. Von dieser erhält sie alle Triggersignale in codierter Form. Nach der Decodierung werden die benötigten Signale an die Detektortriggerempfänger weitergesandt. Dies geschieht mittels des zweiten Bussystems, dem Detektortriggerbus. Beide Systeme sind als differentieller Niederspannungsbus aufgebaut. Dadurch reduziert sich der Stromverbrauch der Module erheblich und infolgedessen auch die Wärmeabgabe aufgrund von Verlustleistung. Der Detektortriggerbus dient zur

<sup>&</sup>lt;sup>8</sup>Steuerungs und Auslese Modul; Ein an der GSI entwickeltes VME Modul zur Steuerung und Auslese von Detektoren.

Verbindung von Detektortriggereinheit und Konzentrator. Wie über den HADES - Triggerbus werden über diesen die Ereignisnummer, die Triggernummer und die Triggerentscheidung übertragen. In der Gegenrichtung, also vom Konzentrator zur Detektortriggereinheit, werden Informationen über den Status der Auslese ("Beschäftigt""Fehler" etc.) übermittelt.

# Kapitel 4

# Realisierung des Konzeptes

## 4.1 Das Motherboard

#### 4.1.1 Aufgabe des Motherboards

Das Motherboard ist die wichtigste Komponente im Auslesesystem der HADES Driftkammern. Seine Aufgabe ist die Digitalisierung der Driftzeit. Hierzu befinden sich auf dem Motherboard TDC - Chips, die speziell zu diesem Zweck entwickelt wurden. Kapitel 5 beschreibt die Funktionsweise des TDC's. Das Motherboard muß auch die gesamte Infrastruktur für den Betrieb der Daughterboards bereitstellen, da diese direkt mit den Motherboards verbunden sind. Neben den Versorgungsspannungen gehört dazu auch eine Schwellenwertspannung für die Diskriminatoren. Abschnitt 4.1.2 beschreibt den dafür verwendeten Digital - zu - Analog - Konverter (DAC). Ein weiterer Abschnitt befaßt sich mit der Schnittstelle zwischen TDC-Kette und Auslesesteuerungseinheit.

#### 4.1.2 Aufbau des Motherboards

Die maximal mögliche Größe des Motherboards wird durch den vorhandenen Platz auf den Seitenrahmen der Driftkammern bestimmt. Grund für die Montage der Motherboards auf den Driftkammerrahmen ist die Bedingung, daß die Karten komplett im Schatten der Magnetspulen liegen sollen. Dadurch soll verhindert werden, daß ein Teilchen beim Durchfliegen des Motherboards durch Vielfachstreuung (siehe 4.2) abgelenkt und dadurch für die weitere Untersuchung unbrauchbar wird. Da die seitliche Rahmenbreite der Driftkammern der Ebene I und II schmaler als 40,0 mm sind, können die Motherboards nur "aufrechtstehend" auf den Rahmen positioniert werden. Zwischen Driftkammerebene I und RICH ist Platz für eine Karte von maximal 44,0 mm Breite. Bei den Ebenen III und IV ist das Platzproblem weitaus unkritischer. Hier ist meistens Platz für bis zu 50,0 mm breite Karten.

Die Länge der Karte hängt von der Anzahl der auf den Rahmen unterzubringenden Analogkarten ab. Zum anderen erfordert die Unterbringung von 8 bzw. 12 TDC-Chips eine Mindestlänge, die garantiert, daß sich die notwendige Verschaltung realisieren läßt. Diese liegt für ein Motherboard mit 64 Kanälen bei ca. 200 mm und für eines mit 96 Kanäle bei ca. 300 mm. Für 8 TDC - Chips wird aufgrund ihrer Größe von  $16 \cdot 16 \text{ mm}^2$  eine Länge von 128 mm benötigt. Bei 12 Chips muß die Mindestlänge 192 mm betragen. In diesen Längen ist noch nicht der Platz für die benötigten Koppelkondensatoren an der Spannungsversorgung jedes Chips einbezogen. Zusätzlich wird noch Platz für die Schnittstelle zur Auslesesteuerungseinheit benötigt. Die Abmessungen des Motherboards betragen insgesamt 240 mm \* 40 mm.

Vorgesehen ist die einseitige Bestückung der Boards mit allen Elektronikkomponenten, damit die zweite Seite weitgehend für den Anschluß der Daughterboards frei ist. Jedes Daughterboard wird über zwei Stecker angeschlossen. Die Signalleitungen werden direkt an die Eingänge des TDC geführt.

Auf der Komponentenseite befindet sich neben den TDC - Chips noch ein Clock - Chip für den von den TDC - Chips benötigten 5 MHz Takt (siehe Kapitel 5). Dazu kommt noch der DAC, der die Schwellenspannungen für die Daughterboards erzeugt, und eventuell Treiberstufen für diese Spannungen, falls die Daughterboards mehr Strom am Schwellenspannungseingang ziehen als der DAC liefern kann.

Die Erdung wird über die Befestigungsstruktur vorgenommen. Dadurch werden alle verwendeten Spannungsversorgungen über einen gemeinsamen Punkt geerdet. Ergebnis ist eine starke Unterdrückung von Störungen, die über die Spannungsversorgung einstreuen. Dabei ist darauf zu achten, daß keine Erdungsschleifen zum Eingang der Analogverstärker entstehen. Ansonsten können die hochempfindlichen Verstärker der Analogkarten durch Stromschwankungen auf den Versorgungsleitungen der Motherboards gestört werden.

#### Der DAC

Für jede der am Motherboard angeschlossenen Analogkarten wird eine Grenzwertspannung benötigt. Um diese Variable halten zu können, befindet sich auf dem Motherboard ein Digital - zu - Analog - Konverter (DAC). Dieser erzeugt anhand einer vorgegebenen Referenzspannung die nötigen Spannungen in Abhängigkeit der eingestellten Werte. Der DAC wird von einem Rechner angesteuert, wodurch eine Anpassung der Schwellenspannung während des laufenden Experimentes möglich ist.

#### Schnittstelle zur Auslesesteuerungseinheit

Die Entfernung zwischen Motherboard und Auslesesteuerungseinheit beträgt bis zu 4 Meter. Die Schnittstelle muß also einerseits in der Lage sein, diese Entfernung zuverlässig zu überbrücken, und soll anderseits nicht zu viele Leitungen enthalten. Die Anzahl der Leitungen wird durch die Zahl der zu übertragenden Signale bestimmt. Um die Übertragungssicherheit zu erhöhen, wird jedes Signal differentiell mit einem LVDS¹ Treiber übertragen. Um die Anzahl der benötigten Leitungen zu verringern, wird ein Multiplexer eingesetzt. Dadurch wird es möglich, eine Leitung für mehrere Signale zu nutzen. Die Anzahl der benötigten Datenleitungen reduziert sich damit auf fünfzig. Der Multiplexer befindet sich zusammen mit den Bustreibern auf einer kleinen Aufsteckkarte. Diese wird neben die Analogkarten auf das Motherboard aufgesteckt und ist mit diesem über zwei Stecker verbunden.

Für die Spannungsversorgung der Motherboards muß eine eigene Leitung verlegt werden. Es ist vorgesehen, diese Leitung auf dem Rahmen des Detektors zu verlegen mit Stichleitungen zu den einzelnen Motherboards.

# 4.2 Plazierung der Front - End - Elektronik

## 4.2.1 Anordnung der Motherboards

#### **Problemstellung**

Neben den Beiträgen zur Entwicklung der Ausleseelektronik wurden paralell dazu auch Überlegungen zur Plazierung dieser Elektronik durchgeführt. Dabei sind Konzentrator und Detektortriggereinheit unkritisch, da sie in VME - Überrahmen untergebracht sind, die außerhalb des Spektrometers angebracht sind. Die Auslesesteuerungseinheiten sind in Überrahmen im Haupttragrahmen aufgehängt. Einzig die Kombination von Motherboard und Daughterboard ist kritisch, besonders zwischen erster Driftkammerebene und RICH und zwischen erster und zweiter Ebene. Zwei Punkte begrenzen hier die Anordnung besonders. Zum einen der verfügbare Platz und zum anderen die möglichen Längen der Kabel zur Zuführung der Analogsignale.

#### Einschränkungen durch vorhandenen Platz

Der kürzeste Abstand zwischen dem Rahmen der ersten Driftkammerebene und dem RICH - Spiegel beträgt 44 mm. In diesem Bereich ist es nicht möglich, die Motherboards in mehreren Ebenen anzuordnen. Gleichzeitig befinden sich in diesem Bereich die meisten Anschlüsse für die Analogsignale. In Abbildung 4.2 sind

$<sup>^1\</sup>mathbf{Low}$  Voltage Differential Signaling - Signalübertragung mit differentiellen Niederspannungspegeln.

Abbildung 4.1: Die Motherboards werden auf dem Aluminiumrahmen der Driftkammern montiert. Gezeigt sind die Kammern der Ebenben I und II.

die Anschlüsse der Signaldrähte einer Seite eines Moduls der Driftkammerebene I gezeigt. Jeder dieser Anschlüsse führt jeweils vier Signaldrähte nach außen. Die Signaldrähte sind dabei gegeneinander durch Erdungsanschlüsse abgeschirmt. Wie man aus der Häufung der Anschlüsse am unteren Ende des Detektors, also in der Nähe des Strahls, erkennen kann, erwartet man hier die meisten Daten. In diesem Bereich müssen also die meisten Motherboards montiert werden. Auf der Abbildung ist auch zu sehen, wie eine mögliche Anordnung der Motherboards aussehen könnte. Das Motherboard in der dritten Ebene muß aus Platzgründen auf der Rückseite des Detektors montiert werden. Legt man für alle Motherboards eine Breite von 40 mm zugrunde, reicht der Platz für diese Konfiguration aus. Zur Seitenbezeichnung und Reihenfolge der Signaldrahtebenen siehe auch Abschnitt 2.4. Unter "Auslese" wird im folgenden die Verbindung der Drahtebenen über flexible Folienkabel mit der Elektronik verstanden.

Abbildung 4.2: Die Seitenansicht des Driftkammermodules zeigt die Anordnung der Anschlüsse der Signaldrähte.

#### Einschränkungen durch Kabellängen

Die Länge der Verbindungskabel zwischen Driftkammer und Daughterboard wird von der relativen Entfernung zwischen Kammeranschlußpunkt und Daughterboard bestimmt. Die Anschlüsse auf der Kammer verteilen sich für die Ebenen I und II nur über drei Seiten. Auf der kürzesten Seite befinden sich keine Anschlüsse, da diese Seite nicht lang genug ist, um ein Motherboard aufnehmen zu können. Auf der dieser Seite gegenüberliegenden Seite werden alle dort erreichbaren Signaldrähte zur Auslese herausgeführt. Auf den übrigen beiden Seiten werden alle noch verbleibenden Signaldrähte ausgelesen. Infolgedessen müssen nicht auf der gesamten Länge der Seite Drähte jeder Signalebene ausgelesen werden. Dadurch ergeben sich fünf Bereiche, in denen jeweils unterschiedliche Ebenen ausgelesen werden. Abbildung 4.3 verdeutlicht den Zusammenhang zwischen den Auslesezonen. Im Bereich C1 auf der rechten Seite der Driftkammer werden nur die Drähte der 0° Ebene ausgelesen, da alle hier befestigten Drähte der + 20° und + 40° Ebenen im Bereich B ausgelesen werden. Im Bereich C2 müssen zusätzlich noch die Drähte der + 20° Ebene ausgelesen werden, da diese nun nicht mehr im Bereich B ausgelesen werden können. Im Bereich C3 gilt dies auch für die Drähte der + 40° Ebene. Da auf der kurzen Seite A keine Signaldrähte ausgelesen werden, kommen im Bereich C4 die Drähte der - 40° Ebene dazu und im Bereich C5 die der - 20° Ebene. Für die linke Seite gilt das gleiche nur mit umgekehrten Vorzeichen bei den Winkeln. Tabelle 4.1 gibt die Anzahl der Signaldrähte je Auslesezone für die Driftkammermodule I und II an.

Die Verbindung zwischen Driftkammer und Daughterboard wird über Folienkabel hergestellt. Da die verwendeten Kabel keine Abschirmung haben, sind sie sehr empfindlich für äußere Störungen. Daher wird angestrebt, sie so kurz wie möglich zu halten. Der Anschluß dieser Kabel an die Driftkammer wird bei den Modulen der Ebenen I und II unterschiedlich vorgenommen.

Bei den Modulen der Ebene II werden die Drähte der Kammer auf speziell gefertigten Platinen fixiert und auf Leiterbahnen kontaktiert, die die Signale

Abbildung 4.3: Auslesezonen der Driftkammern. In den fünf mit C1 bis C5 bezeichneten Bereichen werden jeweils unterschiedliche Ebenen Ausgelesen.

nach außen führen. Diese Platinen werden mit Stesalitrahmen als Abstandshalter zusammengesetzt und bilden den Seitenrahmen der Kammer. Die Folienkabel werden mit aufgekrimpten Lötsteckern auf diese Platinen gelötet und dadurch mit den Signaldrähten verbunden.

Hingegen sind die Signaldrähte bei der Ebene I schon auf Folienkabel gelötet, welche in die Stesalitrahmen eingeklebt sind. Zu diesem Zweck sind entsprechende Vertiefungen in die Rahmen gefräst. Die Kabel enden in zwei

| Anzahl der Signaldrähte je Auslesezone |     |    |     |    |    |    |

|----------------------------------------|-----|----|-----|----|----|----|

|                                        | В   | C1 | C2  | С3 | C4 | C5 |

| Modul 1                                | 312 | 50 | 102 | 83 | 90 | 50 |

| Modul 2                                | 284 | 47 | 98  | 97 | 88 | 63 |

Tabelle 4.1: Anzahl der Signaldrähte pro Auslesezone für die Driftkammermodule I+II

um 90° abgewinkelten Fingern, auf denen sich jeweils die Anschlüsse für vier Signaldrähte befinden. Auch hier liegt zwischen den Signalanschlüssen jeweils ein Erdungskontakt. Auf diese Lötkontakte wird nun jeweils ein weiteres Folienkabel mit aufgekrimptem Stecker gelötet.

Wie Abbildung 4.2 zeigt, werden die Anschlüsse gleichmäßig über den möglichen Bereich herausgeführt. Das erschwert allerdings die Verbindung zum Daughterboard, weshalb hier die flexiblen Folienkabel verwendet werden. Dabei kommt es durch den seitlichen Versatz zwischen Anschlußpunkt und Daugtherboardstecker zu Verdrehungen der Kabel.

#### 4.2.2 Bus zur Auslesesteuerungseinheit

#### Anzahl der Bussysteme

An eine Schnittstelle der Auslesesteuerungseinheit können bis zu zwei Motherboards angeschlossen werden. Da nicht alle Motherboards bei einem Ereignis gleichviele Signale sehen, unterscheidet sich die Datenmenge, die pro Ereignis über jedes Bussystem übertragen wird. Um eine Angleichung der Belastung der Systeme durchzuführen, werden Motherboards mit geringer Datenmenge zu Paaren zusammengeschaltet. Unter Berücksichtigung der Ergebnisse der Simulationen aus dem nächsten Abschnitt führt das zu zehn Bussystemen pro Detektor. Diese sind in Abbildung 4.4 für ein Driftkammermodul dargestellt.

Dabei kommen zwei verschiedene Boardgrößen zum Einsatz. Dort wo die höchsten Datenraten erwartet werden, werden Boards mit nur 64 - TDC Kanälen verwendet. Dies ist der Bereich in der Nähe zum Strahl. Im übrigen Bereich kommen sofern nötig Boards mit 96 - Kanälen zur Verwendung. Im Auslesebereich B, der am weitesten von der Strahlachse entfernt ist, werden je zwei Boards (96 und 64 Kanäle) zusammengeschaltet. Auf den Seiten der Kammer werden zwei Boards mit 96 Kanälen zusammengeschaltet. Dadurch reduziert sich die Anzahl von 14 Bussystemen, wenn jedes Motherboard für sich ausgelesen wird, auf zehn Bussysteme.

#### Simulationen zur Busauslastung

Um zu ermitteln, wieviele Treffer jedes Motherboard pro Ereignis registrieren wird, war die Durchführung von Simulationen unerläßlich. Als Grundlage dieser Simulationen wurden Ereignisse des HADES - Event - Generators<sup>2</sup> verwendet. Simuliert wurden Au + Au Kollisionen bei 1AGeV. Aus diesen Daten wurde die Nummer des Drahtes berechnet, der von einem Teilchen ein Signal sieht. Als Ergebnis dieser Rechnung erhält man die Anzahl der Teilchen für jeden Draht,

$<sup>^2\</sup>mathrm{HADES}$ - Ereignis - Generator: Programm, das aufgrund von Modellen die Spuren von Teilchen aus Stoßprozessen berechnet

Abbildung 4.4: Zehn Auslesebussysteme sind pro Driftkammermodul notwendig. Dabei werden einige Motherboards zusammen über ein Bussystem ausgelesen.

gemittelt über 100 Ereignisse.

Um ermitteln zu können, welches Motherboard nun wieviele Signale sieht, muß zunächst eindeutig festgelegt werden, welches Motherboard welche Signaldrähte ausliest. Dazu wurden zunächst Zeichnungen von allen Signalebenen angefertigt. Aus diesen Zeichnungen wurde die Anzahl der Drähte pro Ebene per abzählen gewonnen. Damit war die Anzahl der benötigten Daughterboards und damit auch der Motherboards festgelegt. Dabei wurde berücksichtigt, daß die endgültigen Module eventuell einige Drähte mehr haben könnten als hier ermittelt. Dazu wurden an den Ecken des Detektors nur zwei Signaldrähte pro Anschlußpunkt zur Auslese herausgeführt. Insgesamt benötigt die Auslese der Driftkammerdrähte 14 Motherboards. Wie diese angeordnet sind, zeigt Abbildung 4.4. Mittels Zeichnungen, wie Abbildung 4.2, wurde dann die Zuordnung zwischen Signaldraht und Motherboard festgelegt. Die Zuordnungsinformationen wurden als Datei auf dem Rechner abgelegt, wobei sie in Form einer Datenbank organisiert wurden. Dies geschah im Hinblick auf eine später mögliche Übernahme in die HADES - Datenbank.

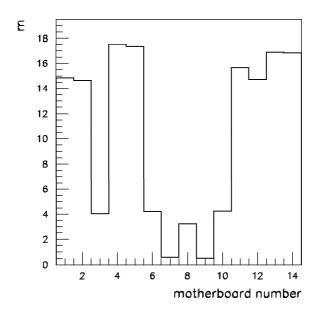

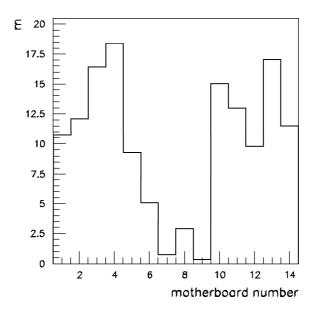

Abbildung 4.5 und 4.6 zeigen die Ergebnisse der Simulationen für die beiden inneren Driftkammerebenen. Aufgetragen ist die Anzahl der Datenworte pro Mo-

Abbildung 4.5: Busauslastung Driftkammerebene I

therboard gemittelt über 100 Au + Au Ereignisse. Ein Vergleich mit Abbildung 4.4 zeigt, daß die geringsten Datenraten im Auslesebereich B zu erwarten sind. Dies beruht auf der erwarteten Winkelverteilung der Dielektronen. Detaillierte Angaben hierzu findet man in [Sch95] und [Kar93]. Es zeigt sich, daß selbst im Bereich der höchsten Multiplizität nicht mit mehr als 20 Datenworten pro Motherboard gerechnet werden muß. Diese Zahl ist die Grundlage für die Konzeption des Auslesekonzeptes in Bezug auf Bandbreiten von Bussystemen.

In Abbildung 4.5 und 4.6 ist äuffällig, daß die Datenraten auf den Motherboards sechs und sieben sowie acht und neun nicht entsprechend der Geometrie der Anordnung symmetrisch sind. Ursache für diese Asymmetrie ist die nicht gleichmäßige Zuordnung der vier hier auszulesenden Signalebenen zu den Motherboards.

### 4.3 Kühlung der Komponenten

Beim Betrieb elektronischer Schaltungen wird immer ein Teil der aufgenommenen Leistung in Form von Wärme abgegeben (Verlustleistung). Für die Kombination aus Mother- und Daughterboard stellt die dadurch verursachte Erwärmung der Umgebungsluft ein Problem dar. Da die Meßeinheit des TDC temperaturabhängig ist, muß die entstehende Wärme abgeführt werden. Der Haupteil der Verlustleistung wird von den benötigten differentiellen Leistungstreibern abgegeben, nämlich 2,5 W pro Stück bei 5 V Versorgungsspannung. Jeder TDC - Chip setzt etwa 430 mW an Leistung um. Somit wird pro Motherboard  $\approx 10$  W an Leistung umgesetzt. Die Daughterboards setzen  $\approx 600$  mW pro Karte um. Die insgesamt umgesetzte Leistung beträgt für ein Board mit 64 Kanälen 13,2 W und

Abbildung 4.6: Busauslastung Driftkammerebene II

für ein Board mit 96 Kanälen 14,9 W. In diesen Rechnungen ist die Leistungsaufnahme des Logikchips der Schnittstellen zur Auslesesteuerungseinheit noch nicht enthalten, da sie im Datenblatt des Herstellers nicht angegeben ist. Die gesamte Leistung der Driftkammerelektronik direkt am Detektor beträgt damit  $\approx 5$  kW. Zur Kühlung der Komponenten stehen zwei Verfahren zur Auswahl. Entweder wird die Kühlung durch einen Luftstrom der kontinuierlich über die Oberfläche der Komponenten streicht, vorgenommen, oder man setzt auf die Komponenten Kühlkörper mit einer aktiven Wasserkühlung. Für die Ausleseelektronik der Driftkammern scheidet die aktive Wasserkühlung aus mehreren Gründen aus. Zum einen bedeutet das Anbringen von Kühlkörpern das Einbringen von zusätzlichem Material, und damit einer weiteren Quelle von Sekundärelektronen. Zudem würde ein Defekt im Kühlsystem einen großen Schaden anrichten.

Es kommt also nur die Kühlung durch einen Luftstrom in Betracht. Dieser Luftstrom muß aber auf den Bereich der Elektronik begrenzt werden. Das kann z.B. durch Anbringen einer Folie um die Elektronik herum geschehen.

### Kapitel 5

## Der HADES TDC - Chip

### 5.1 Anforderungen an den TDC

Tabelle 5.1 faßt die Spezifikationen des TDC - Chips zusammen<sup>1</sup>. Grundlage für diese Spezifikation sind zum einen die Eigenschaften der Driftkammer (Ortsauflösung etc.) und zum anderen die Anforderungen des Triggersystems (Ereignisraten etc.). Die Rate der Triggersignale der ersten Triggerstufe von  $10^5$  pro Sekunde erfordert eine Digitalisierung der Driftzeiten und die Auslese innerhalb von  $10\mu$ s. Da die Signale der Driftkammern nur etwa 20 mA stark sind soll die Digitalisierung so nahe wie möglich am Detektor stattfinden. Dazu ist eine hohe Integration der Meßelektronik erforderlich wie die Ausführungen über das Platzproblem im vorigen Kapitel gezeigt haben.

#### 5.2 Der funktionelle Aufbau

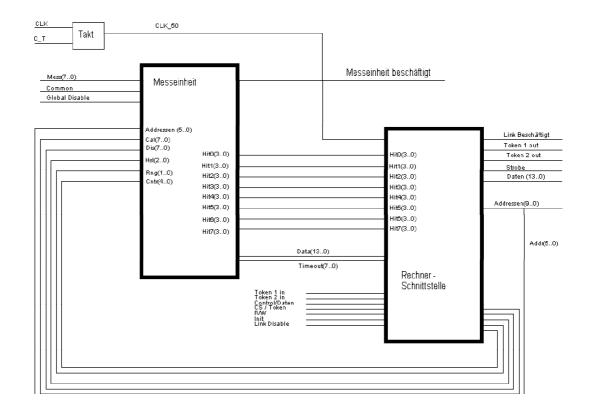

Der TDC - Chip besteht aus zwei funktionell unabhängigen Teilen: zum einen dem Zeitmeßteil und zum anderen der Rechnerschnittstelle. Abbildung 5.1 zeigt ein Blockschaltbild des TDC's. In den folgenden Abschnitten sollen Meßeinheit und Rechnerschnittstelle ausführlich beschrieben werden. Zunächst wird ein Überblick über das Zusammenspiel der beiden Komponenten gegeben.

Die Meßeinheit erhält von außen die Signale zum Starten und Anhalten der Zeitmessung über die Eingänge "Mes(7..0)" und "Common". Jeder der "Mes"- Eingänge ist auf einen eigenen Meßkreis geschaltet, während der "Common"- Eingang auf alle Meßkreise gleich wirkt. Mit dem Signal "Global Disable" ist es möglich, die Eingänge der Meßeinheit zu sperren. Um Störungen der Auslese zu vermeiden, kann dieser Eingang mit dem "Beschäftigt"- Ausgang der Rechnerschnittstelle verbunden werden. Damit wird verhindert, daß die Meßeinheit die Meßwerte während der Auslese überschreibt. Da während der Auslese allerdings durch die

<sup>&</sup>lt;sup>1</sup>Zu den TDC - Spezifikationen vergleiche auch [Hof95] und Kapitel 6

| TDC Spezifikationen |                          |                            |  |

|---------------------|--------------------------|----------------------------|--|

|                     | Nach GSI Spezifikation   | Nach Messungen             |  |

| Auflösung           | $\leq 500 \mathrm{ps}$   | $220 \pm 1 \text{ ps}$     |  |

| Differentielle      | $\leq 300 \mathrm{ps}$   | Nicht gemessen             |  |

| Nichtlinearität     |                          |                            |  |

| maximales Intervall | $\leq 1024 \text{ns}$    | $\approx 4\mu \text{ s}$   |  |

| Kanäle pro Chip     | 8                        | 8                          |  |

| Common Mode         | Common Stop              | Common Stop                |  |

| Auto reset          | bei Full Range ohne Stop | Reset nach Erreichen       |  |

|                     | Signal                   | einer einstellbaren Grenze |  |

| Nullunterdrückung   | vorhanden                | vorhanden                  |  |

Tabelle 5.1: Vergleich der TDC - Spezifikationen mit den Ergebnissen der TDC - Tests

Abbildung 5.1: Blockschaltbild des TDC's. Die Trennung zwischen Meßeinheit und Rechnerschnittstelle wird an diesem Bild deutlich. Nach [Gle96]

Detektortriggereinheit die Erzeugung weiterer Triggersignale der ersten Triggerstufe unterbunden wird (vgl. 2.2), kann das "Global Disable"- Signal auch über den Auslesekontroller gesetzt werden. Die Kommunikation der Meßeinheit geschieht nur über die Rechnerschnittstelle.

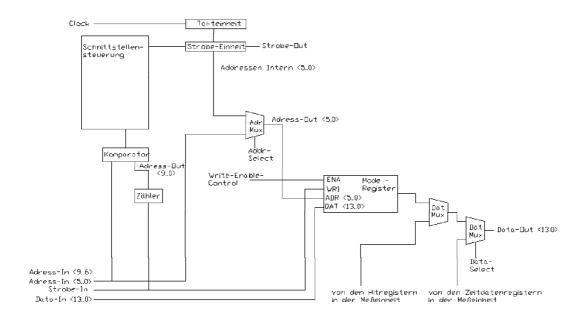

Von der Rechnerschnittstelle werden die "Daten(13..0)"- und die "Adressen(9..0)"- Leitungen nach außen geführt. Dazu kommen noch die Steuerleitungen ("Token-1-In", "Token-2-In", "Control/Daten", "Chip Select/Token", "Read/Write", "Init", "Link disable", "Link beschäftigt", "Token-1-Out", "Token-2-Out", "Strobe"). Die Daten- und Adressleitungen sind als Tristate - Treiber im Chip ausgelegt. Das bedeutet, daß sie entweder als Eingang oder als Ausgang geschaltet werden können. Zwischen diesen Modi schaltet man über die Leitung "Read/Write" um. Mit dem Signal "Link Disable" ist es möglich, alle Daten- und Adressleitungen in den dritten Zustand zu schalten. In diesem sind sie hochohmig gegen Masse abgeschlossen, wodurch Signale auf diesen Leitungen keinen Einfluß auf die Rechnerschnittstelle mehr haben.

### 5.3 Das Meßprinzip

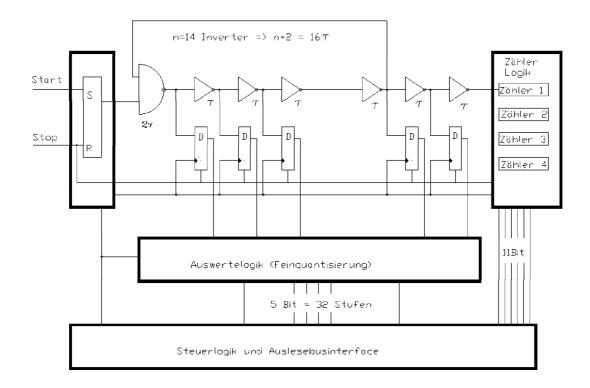

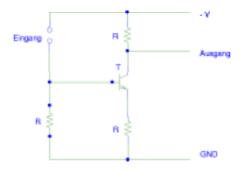

Die Meßeinheit ist vom Prinzip identisch mit derjenigen des in [Git94] beschriebenen TDC2001. Es nutzt die Signallaufzeiten in Halbleiterschaltungen aus. Abbildung 5.2 zeigt das verwendete Schaltungsprinzip. Kernstück dieser Schaltung ist eine Kette von Invertern(siehe Anhang A). In diese Kette wird der Puls am Meßeingang des Meßkreises eingespeist. Da die Anzahl der Inverter in der Kette ungerade ist, ändert der Puls bei jedem Umlauf seine Polarität. Gleichzeitig mit dem Inverter wird auch ein Flip - Flop angesteuert. Dieses wechselt seinen Status entsprechend der Polarität des Pulses. Das Flip - Flop speichert damit die Position des Pulses in der Inverterkette. Mit den Flanken des Signales am letzten Inverter wird ein Zähler gesteuert, der die Umläufe des Pulses zählt. Bei Eintreffen eines Stoppulses wird der Zustand der Flip - Flops eingefroren und der Zähler angehalten. Die Auswertelogik setzt aus dem Stand des Zählers und dem Ergebnis der Feinquantisierung, das durch Abzählen der Flip - Flops mit "0" und "1" Status gewonnen wird, das Meßergebnis zusammen. Dieses wird in einem Register abgelegt. Im Gegensatz zum TDC2001 besitzt der HADES - TDC nur einen Zähler. Seine Fähigkeit mehrere Startsignale vor einem Stopsignal zu verarbeiten ("Multihitfähigkeit") erhält er, indem beim Eintreffen eines weiteren Startsignales eine Meßwertermittlung durchgeführt wird, als wäre ein Stopsignal eingetroffen. Dadurch wird nur eine Information über den zeitlichen Abstand des neuen Startsignals vom ersten Startsignal gewonen. Erst beim Eintreffen des Stopsignals wird die Zeit, die seit dem ersten Startsignal verstrichen ist, im Register abgelegt. Um nun die Zeit zwischen einem zusätzlichen Startsignal und dem Stopsignal zu ermitteln, muß zwischen dem letzten Zeitwert und jeweils einem vorherigen die Differenz gebildet werden.

Abbildung 5.2: Prinzipschaltbild des TDC Messkreises. Nach [Git94]

Realisiert wird dieses Meßprinzip auf einem speziellen Siliziumchip durch zusammenschalten von vorgefertigten Gattern. Jedes Gatter besteht aus mehreren fest verschalteten Transistoren und führt eine bestimmte logische Funktion (AND, OR NAND usw.) aus. Die Signallaufzeiten eines Inverters, bestimmen das Binning des TDC's. Durch die Bildung einer Kette von Invertern mitteln sich die durch unterschiedliche Signallaufzeiten verursachten Fehler im Ergebnis aus.

Der Vorteil des verwendeten Meßprinzips liegt in der fehlenden Konversionszeit. Ein TDC nach dem sonst verwendeten Prinzip, bei dem die Eigenschaften eines Kondensators ausgenutzt werden, hätte im Rahmen des HADES - Auslesekonzeptes zu langen Totzeiten und damit zum Verlust von Ereignissen geführt. Ein weiterer Vorteil des verwendeten Meßprinzips ist die hohe Integrationsdichte. Erst diese ermöglicht den Einsatz des TDC's direkt am Detektor, wo wenig Platz zur Verfügung steht. Das Meßprinzip wurde erst durch die Erhöhung der Integrationsdichte möglich, da die Signallaufzeit proportional zur Größe der Strukturen ist. Nachteil dieses Prinzips ist allerdings eine erhöhte Temperaturund Spannungsabhängigkeit gegenüber den gebräuchlichen Prinzipien.

Abbildung 5.3: Blockschaltbild der TDC - Rechnerschnittstelle. Nach [Gle96]

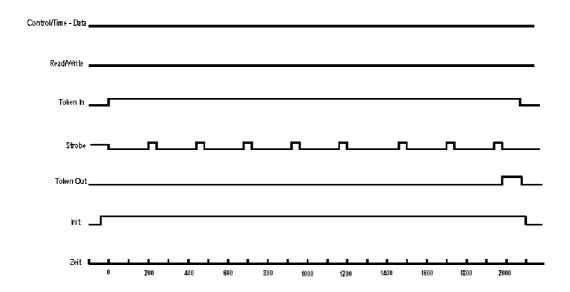

Da die Schaltzeit der Gatter stark temperatur- und spannungsabhängig ist, muß entweder auf die Konstanz dieser Parameter besonders geachtet, oder die Zeitmessung regelmäßig geeicht werden. Dazu besitzt der TDC eine interne Kalibrierungsfunktion. Bei Aktivierung dieser Funktion generiert der TDC aus dem externen Takt vier Pulse gleicher Dauer und Länge. Drei dieser Pulse werden als Startpuls in die Meßeinheit eingespeist. Der vierte Puls stoppt die Meßeinheit. Dadurch erhält man bis zu sechs Hits. Drei für das Triggern auf die erste Flanke und drei für die zweite Flanke.

#### 5.4 Die Rechnerschnittstelle

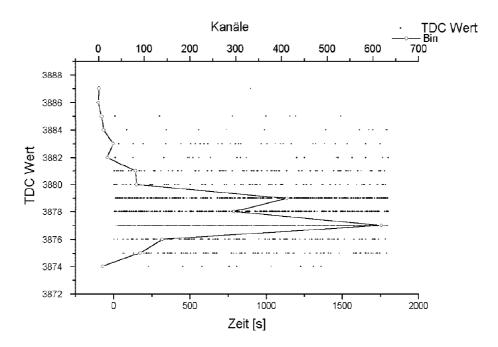

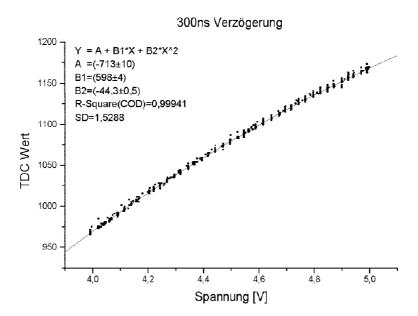

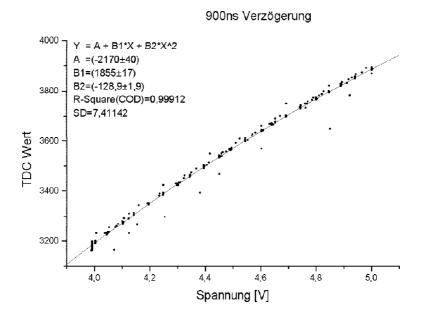

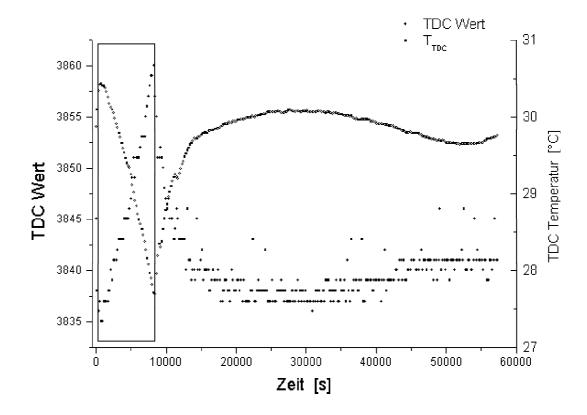

Die Rechnerschnittstelle besitzt vier Initialisierungsregister. Zwei davon bestimmen, welche Kanäle für die Messung bzw. die Kalibrierung freigegeben werden. Mit den beiden anderen Registern werden die Eigenschaften von Meßeinheit und Rechnerschnittstelle konfiguriert. Im Anhang D sind die Initialisierungsregister beschrieben.