# Das Auslesesystem für den Ringabbildenden Čerenkovdetektor im HADES Spektrometer

Diplomarbeit von Michael Böhmer

Fakultät für Physik der Technischen Universität München Physik-Department E12 Dezember 1999

# Zusammenfassung

In der vorliegenden Arbeit wird die schnelle Ausleseelektronik für die 28 000 Kanäle im Photonenzähler des RICH Detektors vorgestellt, die im HADES-Experiment zum Einsatz kommt. Das Auslesesystem ist modular aufgebaut und besteht aus 450 Frontend-Modulen (FE) mit je 64 Verstärkerkanälen und einer A/D-Wandlungseinheit mit Speicher für 120 Ereignisse. Die Auslese der Frontends sowie eine weitere Datenzwischenspeicherung erfolgt über Readout-Controller (RC) mit VME-Busanschluß. Eine Detektortriggereinheit (DTU) steuert die Abläufe im Auslesesystem.

Die hohe Modularisierung und Konfigurierbarkeit des Systems ermöglicht den Einsatz auch an anderen bildgebenden Detektoren, ohne größere Modifikationen an der Hardware vornehmen zu müssen.

Im Rahmen der Diplomarbeit wurde die Entwicklung des RC-Moduls abgeschlossen und ein Prototyp fertiggestellt. Darüberhinaus wurde das FE-Modul in seinem digitalen Teil grundlegend überarbeitet und die DTU mit der noch fehlenden Steuerlogik vervollständigt.

Mit einem Prototypaufbau wurde das Auslesekonzept auf seine Funktionsfähigkeit hin überprüft. Die Zusammenarbeit des Systems mit den anderen Komponenten des HADES-Datenaufnahmesystems konnte im Labor erfolgreich getestet werden. Dabei wurde die Erfüllung der Designkriterien (10  $\mu$ s Datenaufnahmezeit, 10<sup>5</sup> Hz Ereignisrate, 10 bit Digitalisierung und asynchrone Auslese über zwei Pufferstufen) bestätigt.

Nach Abschluß der Tests konnte die Kleinserienproduktion aller Module (FE und RC) begonnen und abgeschlossen werden. In einem ersten Testexperiment mit dem RICH am Schwerionenstrahl der GSI konnten erste Erfahrungen gewonnen werden, über die am Ende der Arbeit berichtet wird.

Zur Ansteuerung der Hardware wurde unter Beachtung der HADES Programmierrichtlinien ein umfangreiches Softwarepaket geschrieben, das eine einfache Schnittstelle zur Ansteuerung der komplexen Funktionen bereitstellt. Auf Grundlage dieser Bibliothek können nicht nur Programme zur Konfiguration des Auslesesystems geschrieben werden; eine einfache Integration der Steuerungsfunktionen in die slow control-Software EPICS wird dadurch ermöglicht.

# Inhaltsverzeichnis

| 1 | $\mathbf{Ein}$ | leitung und Motivation                           | 1  |

|---|----------------|--------------------------------------------------|----|

|   | 1.1            | Physikalische Zielsetzung                        | 1  |

|   | 1.2            | Aufbau und Anforderungen des HADES Spektrometers | 3  |

|   | 1.3            | Der RICH-Detektor                                | 4  |

| 2 | Das            | HADES Auslese- und Triggerkonzept                | 7  |

|   | 2.1            | Das Triggersystem                                | 8  |

|   | 2.2            | Die LVL1-Pipe                                    | 9  |

|   | 2.3            | Die LVL2-Pipe                                    | 10 |

|   | 2.4            | Speicherung in der DAQ                           | 10 |

| 3 | Das            | RICH Auslesesystem                               | 11 |

|   | 3.1            | Erwartete Datenmengen                            | 11 |

|   | 3.2            | Weitere Anforderungen                            | 13 |

|   | 3.3            | Einbindung in das HADES-Triggerkonzept           | 14 |

|   | 3.4            | Technische Realisierung                          | 15 |

|   | 3.5            | Auswahl der verwendeten Technologie              | 16 |

|   |                | 3.5.1 Standardkomponenten                        | 17 |

|   |                | 3.5.2 CPLDs                                      | 18 |

|   |                | 3.5.3 Microcontroller                            | 18 |

|   |                | 3.5.4 ASICs                                      | 19 |

|   |                | 3.5.5 FPGAs                                      | 20 |

| 4 | Das            | RICH Frontend                                    | 23 |

|   | 4.1            | Aufgaben                                         | 23 |

|   | 4.2            | Blockschaltbild und Funktionsübersicht           | 24 |

|   | 4.3            | Digitalisierung und Zwischenspeicherung          | 25 |

|   | 4.4            | Auslese der Frontend-Module                      | 29 |

|   |                | 4.4.1 Der Frontend-Bus                           | 29 |

|   |                | 4.4.2 Zyklen zur Muster- und Analogdatenauslese  | 31 |

|   |     | 4.4.3 Der Löschzyklus                              | 32 |

|---|-----|----------------------------------------------------|----|

|   | 4.5 | Konfiguration des Frontend-Moduls                  | 32 |

|   |     | 4.5.1 Schreiben der Schwellen                      | 32 |

|   |     | 4.5.2 Lesen der Schwellen                          | 33 |

|   | 4.6 | Busy-Erzeugung                                     | 34 |

| 5 | Der | RICH Readout-Controller                            | 39 |

|   | 5.1 | Aufgaben                                           | 39 |

|   | 5.2 | Blockschaltbild                                    | 40 |

|   | 5.3 | Grundlegendes zur Funktionsweise                   | 40 |

|   |     | 5.3.1 Der /STOP-Modus                              | 42 |

|   |     | 5.3.2 Die Struktur der Datenbusse                  | 42 |

|   |     | 5.3.3 Datenformat                                  | 43 |

|   |     | 5.3.4 Die Mapping-Einheit                          | 44 |

|   | 5.4 | Die Steuerung der Frontend-Auslese                 | 45 |

|   |     | 5.4.1 Grundlegender Aufbau der Auslesesteuerung    | 46 |

|   |     | 5.4.2 Die Schnittstelle zur DTU                    | 48 |

|   |     | 5.4.3 Die Schnittstelle zum Ringerkenner           | 49 |

|   |     | 5.4.4 Die Schnittstelle zur LVL2-Pipe              | 50 |

|   | 5.5 | Zyklen zur Frontend-Auslese                        | 50 |

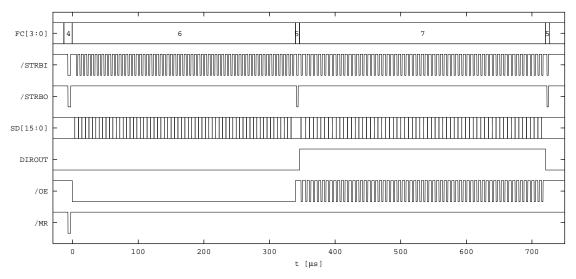

|   |     | 5.5.1 Zurücksetzen der Ausleseelektronik           | 50 |

|   |     | 5.5.2 Musterübertragung zum Ringerkenner           | 52 |

|   |     | 5.5.3 Übertragung von Analogdaten in die LVL2-Pipe | 54 |

|   |     | 5.5.4 Löschen von Analogdaten                      | 55 |

|   | 5.6 | Die LVL2-Pipe                                      | 56 |

|   |     | 5.6.1 Anforderungen                                | 56 |

|   |     | 5.6.2 Abläufe im Memory-FPGA                       | 59 |

| 6 | Die | RICH DTU                                           | 63 |

|   | 6.1 | Aufgaben                                           | 63 |

|   | 6.2 | Blockschaltbild                                    | 64 |

|   | 6.3 | Die Umsetzung der Triggerbus-Befehle               | 65 |

|   |     | 6.3.1 Unterstützte Triggerbus-Befehle              | 65 |

|   |     | 6.3.2 LVL1-Auslesesteuerung                        | 67 |

|   |     | 6.3.3 LVL2-Auslesesteuerung                        | 68 |

|   |     | 6.3.4 Auslese-Arbitrierung                         | 69 |

|   | 6.4 | Busy-Handling                                      | 70 |

|   |     | 6.4.1 LVL1BSY                                      | 71 |

|   |     | 6.4.2 LVL2BSY                                      | 72 |

| 7                | Inb   | etriebn | nahme und Tests                      | <b>73</b> |

|------------------|-------|---------|--------------------------------------|-----------|

| 7.1 Der Prototyp |       |         |                                      |           |

|                  |       | 7.1.1   | Durchgeführte Tests                  | 74        |

|                  |       | 7.1.2   | Erfolgreicher Betrieb im Labor       | 75        |

|                  |       | 7.1.3   | Durchgeführte Verbesserungen         | 75        |

|                  | 7.2   | Die Ko  | ontrollsoftware                      | 76        |

|                  | 7.3   | Das Se  | erien-Modul                          | 78        |

|                  |       | 7.3.1   | Qualitätskontrolle                   | 78        |

|                  |       | 7.3.2   | Einsatz im Experiment                | 79        |

|                  |       | 7.3.3   | Weitere Tests                        | 82        |

| 8                | Aus   | blick   |                                      | 85        |

|                  | 8.1   | Inbetr  | iebnahme des Gesamtsystems           | 85        |

|                  | 8.2   | Möglic  | che Verbesserungen                   | 87        |

|                  |       | 8.2.1   | Modifikation der Frontend-Verkettung | 87        |

|                  |       | 8.2.2   | Erweiterungen in der Fehlerkontrolle | 88        |

|                  | 8.3   | Einsat  | z für andere Systeme                 | 88        |

| $\mathbf{A}$     | Glo   | ssar    |                                      | 91        |

| В                | Reg   | isterbe | eschreibung                          | 97        |

|                  | B.1   | Memor   | ry Map                               | 98        |

|                  |       | B.1.1   | Region 1                             | 98        |

|                  |       | B.1.2   | Region 4                             | 98        |

|                  |       | B.1.3   | Region 5                             | 99        |

|                  | B.2   | Interfa | ice-FPGA                             | 99        |

|                  | B.3   | Memor   | ry-FPGA                              | 103       |

|                  | B.4   | Timing  | g-FPGA                               | 106       |

|                  | B.5   | Port-F  | PGA                                  | 108       |

|                  | B.6   | DTU-I   | FPGA                                 | 110       |

| $\mathbf{Li}$    | terat | urverz  | eichnis                              | 114       |

# Abbildungsverzeichnis

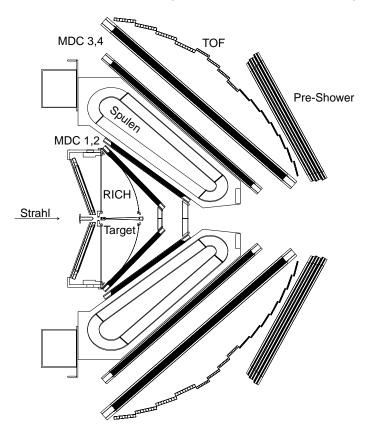

| 1.1 | Schnitt durch das Dileptonenspektrometer HADES   | 3  |

|-----|--------------------------------------------------|----|

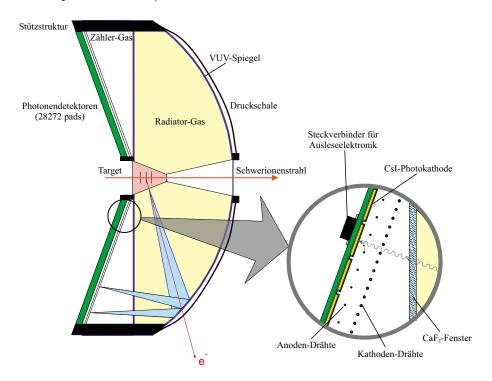

| 1.2 | Schnitt durch den HADES RICH                     | 5  |

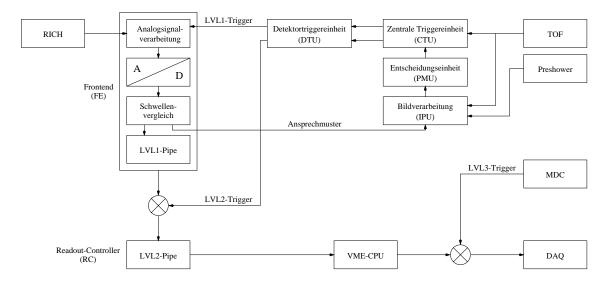

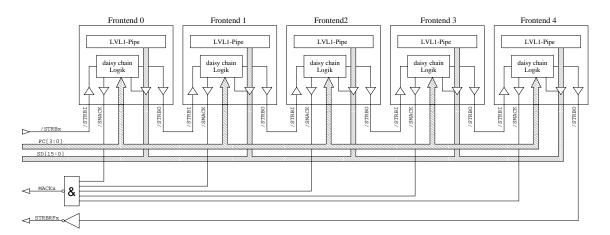

| 3.1 | Auslese- und Triggersystem für den HADES RICH    | 14 |

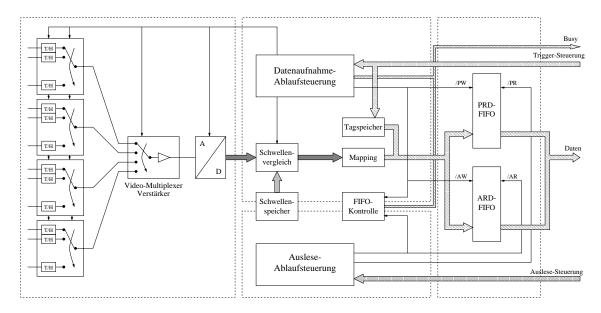

| 4.1 | Blockschaltbild des Frontend-Moduls              | 25 |

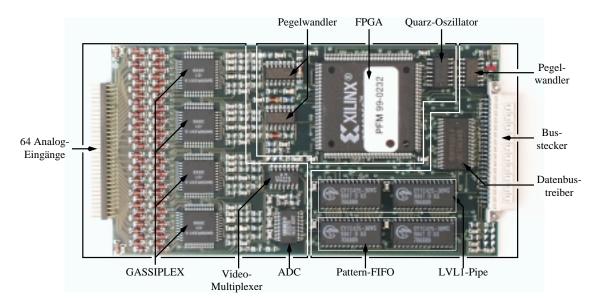

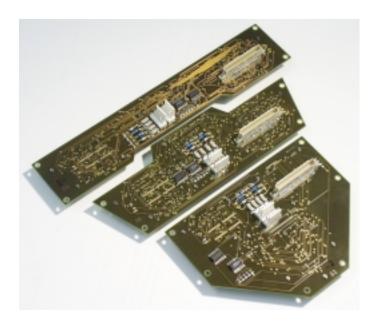

| 4.2 | Layout des RICH Frontend-Moduls                  | 26 |

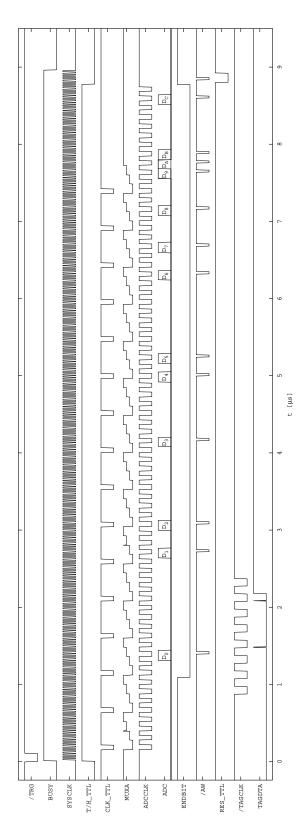

| 4.3 | Datenaufnahmezyklus im Frontend-Modul            | 35 |

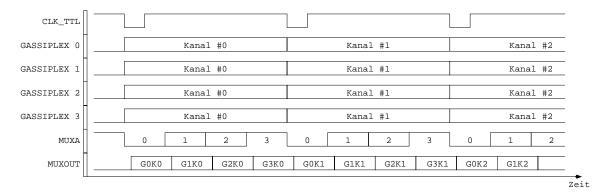

| 4.4 | Multiplex-Verfahren des Frontends                | 36 |

| 4.5 | Blockschaltbild des Frontend-Busses              | 36 |

| 4.6 | Layout einiger Frontend-Busplatinen              | 37 |

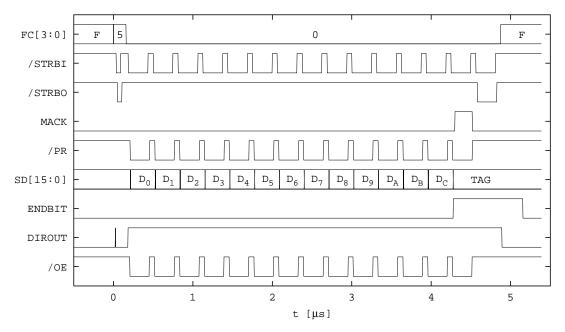

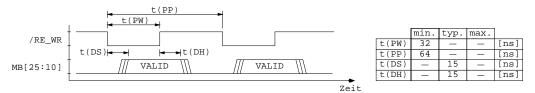

| 4.7 | PRDOUT-Zyklus am Frontend                        | 37 |

| 4.8 | ADELETE-Zyklus am Frontend                       | 38 |

| 4.9 | WCFG- bzw. RCFG-Zyklus am Frontend               | 38 |

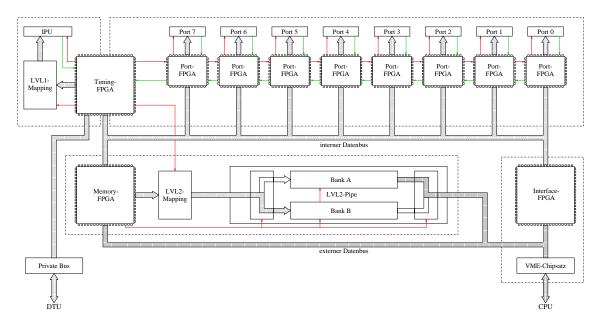

| 5.1 | Blockschaltbild des RICH Readout-Controllers     | 41 |

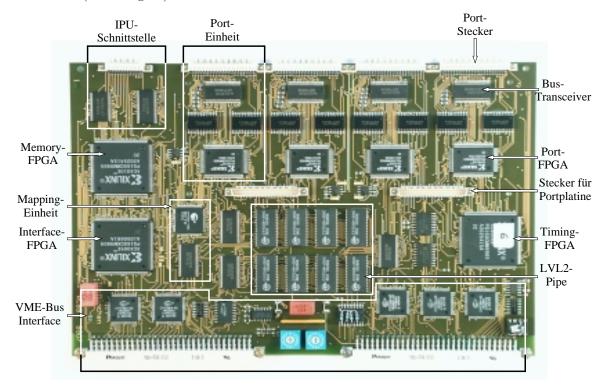

| 5.2 | Layout des RICH Readout-Controllers              | 41 |

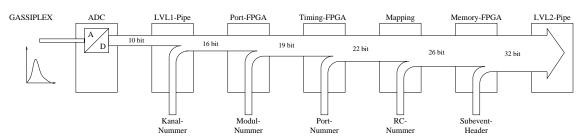

| 5.3 | Datenfluß vom Frontend in die LVL2-Pipe          | 43 |

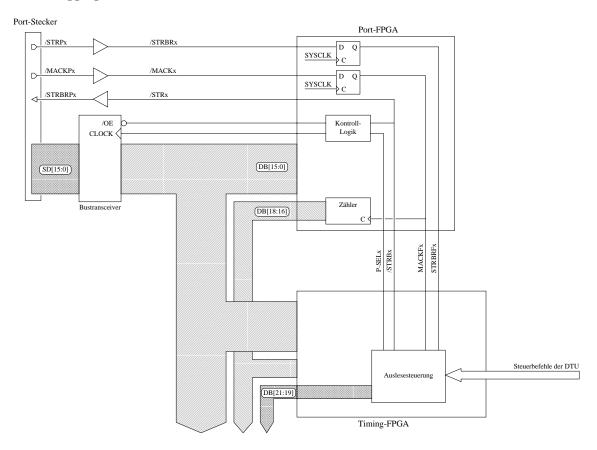

| 5.4 | Blockschaltbild eines Ports                      | 47 |

| 5.5 | Timing-Parameter der IPU-Schnittstelle           | 49 |

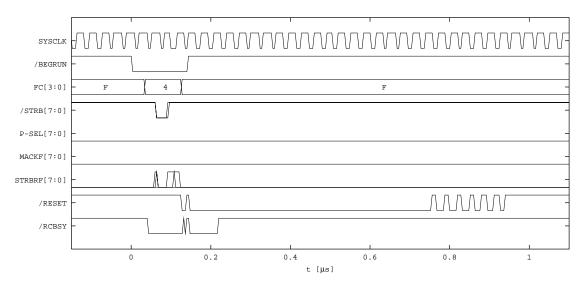

| 5.6 | BEGRUN-Zyklus                                    | 51 |

| 5.7 | PRDOUT-Zyklus aus Sicht des Readout-Controllers  | 52 |

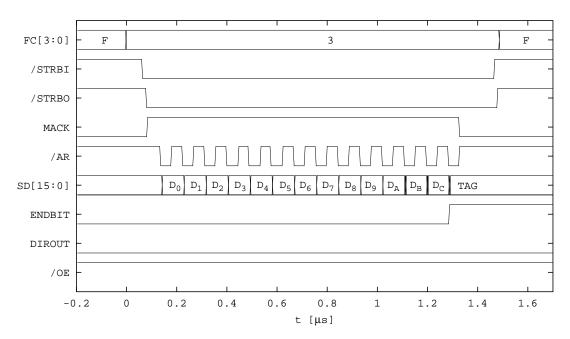

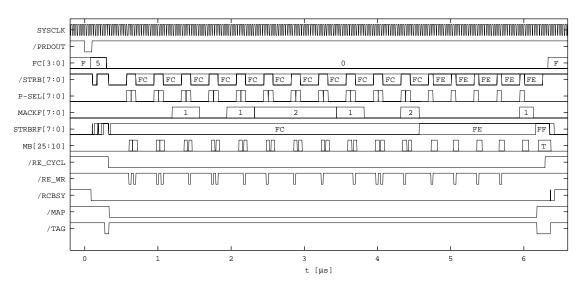

| 5.8 | ARDOUT-Zyklus aus Sicht des Readout-Controllers  | 54 |

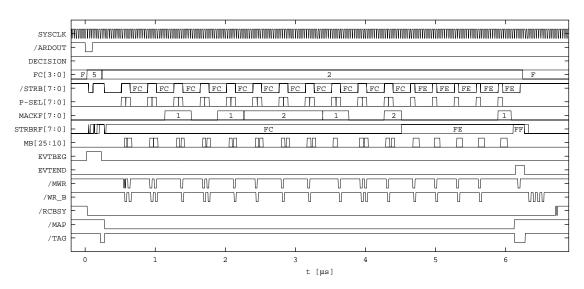

| 5.9 | ADELETE-Zyklus aus Sicht des Readout-Controllers | 55 |

| 6.1 | Blockschaltbild der RICH DTU                     | 64 |

| 6.2 | Timing auf dem Triggerbus                        | 67 |

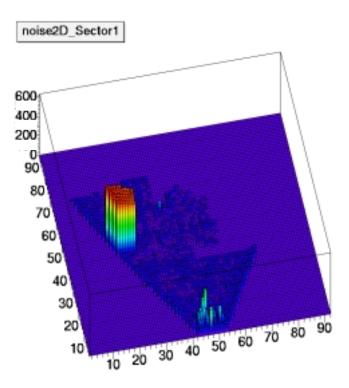

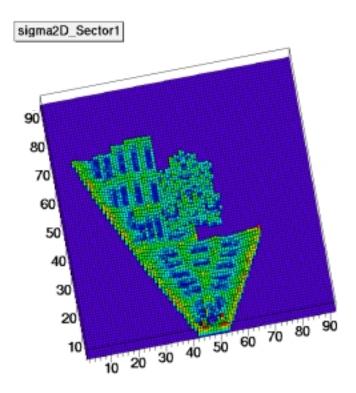

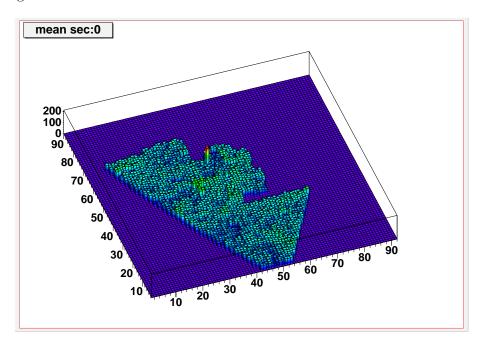

| 7.1 | Off"—line-Analyse der Pedestals                  | 81 |

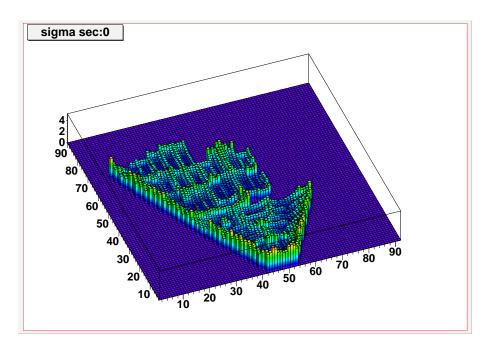

| 7.2 | Off"—line-Analyse des Rauschens                  | 82 |

| 7.3 | Offsetwerte der Frontends nach der Anpassung     | 83 |

| 7.4 | Rauschwerte der Frontends nach der Anpassung     | 84 |

# **Tabellenverzeichnis**

| 1.1 | Eigenschaften der leichten Vektormesonen              | 2  |

|-----|-------------------------------------------------------|----|

| 4.1 | Pinbelegung des Frontend-Bussteckers                  | 27 |

| 4.2 | Signale des Frontend-Busses                           | 29 |

| 4.3 | Übersicht über die Funktionskodes des Frontend-Moduls | 30 |

| 4.4 | Organisation des Schwellenspeichers                   | 33 |

| 5.1 | Datenformat des Readout-Controllers                   | 44 |

| 5.2 | Pinbelegung der Ringerkenner-Schnittstelle            | 50 |

| 5.3 | Struktur eines Subevents                              | 58 |

| 6.1 | Triggerkodes der CTU                                  | 66 |

| B.1 | Region-Übersicht                                      | 97 |

| B.2 | Belegung des Xilinx-Konfigurationsregisters           | 98 |

| B.3 | Aufteilung des Mapping-Speichers                      | 99 |

## Kapitel 1

# Einleitung und Motivation

Ein aktuelles Gebiet in der Kern- und Teilchen-Physik ist die Untersuchung der Eigenschaften von Hadronen in Kernmaterie. Zu diesem Zweck wird momentan an der GSI in Darmstadt das HADES-Experiment aufgebaut, das einen experimentellen Zugang zu diesen Fragestellungen ermöglicht. HADES (High Acceptance Di-Electron Spectrometer) ist speziell auf die Spektroskopie von Elektron-Positron-Paaren ausgelegt, die aus den leptonischen Zerfallskanälen von Vektormesonen stammen.

### 1.1 Physikalische Zielsetzung

Seit geraumer Zeit werden auf der Quantenchromodynamik basierende Modelle diskutiert, die eine Restauration der chiralen Symmetrie bei hoher Temperatur (T > 160 MeV) und Dichte vorhersagen [24], [3]. Als Konsequenz sind Änderungen der Eigenschaften von Hadronen zu erwarten, wenn sie in komprimierter und erhitzter Kernmaterie eingebettet sind. Erste experimentelle Hinweise auf Mediumsmodifikationen liegen bereits vor [1], [28], [23].

Neben Verkürzungen der Zerfallszeit (meßbar über die Vergrößerung der Resonanzbreite) werden Verschiebungen der Polmasse von leichten Vektormesonen  $(\rho, \omega)$  erwartet. Bereits bei Dichte von Kernmaterie im Grundzustand  $(\rho_0)$  sollten meßbare Effekte zu beobachten sein. Beispielsweise können  $\omega$ -Mesonen mit Hilfe eines  $\pi^-$ -Strahls an gebundenen Protonen eines schweren Kerns produziert und die Dielektronen aus dem  $e^+$ - $e^-$ -Zerfallskanal gemessen werden [25], [26].

$$p + \pi^- \rightarrow n + \omega$$

Zur Untersuchung von hadronischer Materie bei höheren Dichten werden zentrale Schwerionenstöße genutzt. So erreicht man beispielsweise bei Au-Au-Stößen im GSI-SIS Energiebereich Dichten von bis zu  $3\rho_0$  und Temperaturen von etwa 50 MeV. In einer zentralen Kollision entsteht dabei ein Feuerball aus dichter und aufgeheizter Kernmaterie, der nach einer charakteristischen Zeit von etwa 10~fm/c expandiert und abkühlt. Bei der vom SIS lieferbaren Strahl-Energie von 1-2~GeV/u entstehen die Vektormesonen  $(\rho,\,\omega,\,\phi)$  überwiegend durch Mehrteilchenstöße (Produktion unterhalb der Schwelle) innerhalb dieses

Feuerballs. Bei der Messung integriert man über Zerfälle zu unterschiedlichen Zeitpunkten und in unterschiedlich dichten Medien, wodurch die Interpretation des so erhaltenen Massenspektrums schwierig wird.

| Meson    | Reichweite $c\tau$ [fm] | Masse [MeV] | Zerfallskanäle                                            | Wahrscheinlichkeit [%]   |

|----------|-------------------------|-------------|-----------------------------------------------------------|--------------------------|

| $\pi^0$  | 251                     | 135         | $\pi^0 \to \gamma \gamma$ $\pi^0 \to e^+ e^- \gamma$      | ~ 99<br>~ 1              |

|          |                         |             | $\frac{\pi^* \to e^+ e^- \gamma}{\eta \to \gamma \gamma}$ | $\sim 1$ $\sim 39$       |

| $\eta$   | 30                      | 547         | $\eta \to \pi^0 \pi^0 \pi^0$                              | $\sim 32$                |

| ρ        | 1,3                     | 770         | $ ho  ightarrow \pi\pi$                                   | ~ 100                    |

|          | ,-                      |             | $ ho  ightarrow e^+ e^-$                                  | $\sim 4.5 \cdot 10^{-5}$ |

| $\omega$ | 23                      | 782         | $\omega \to \pi^+ \pi^- \pi^0$                            | $\sim 89$                |

| ω        |                         |             | $\omega \to e^+ e^-$                                      | $\sim 7.2 \cdot 10^{-5}$ |

| ,        | 44                      | 1 020       | $\phi \rightarrow K^+K^-$                                 | $\sim 50$                |

| $\phi$   |                         |             | $\phi \to K^+ K^-$ $\phi \to K_L^0 K_S^0$                 | $\sim 34$                |

Tabelle 1.1: Eigenschaften der leichten Vektormesonen nach [10].

In Tabelle 1.1 sind die Daten der leichtesten Mesonen aufgeführt; besonders das  $\rho$ -Meson ist wegen seiner kurzen Lebensdauer als Sonde geeignet: die Wahrscheinlichkeit, daß ein innerhalb des Feuerballs gebildetes  $\rho$ -Meson auch dort zerfällt, ist sehr hoch. Das  $\rho$ -Meson besitzt (ebenso wie das  $\omega$ ) einen stark unterdrückten leptonischen Zerfallskanal; das entstehende Leptonenpaar kann die hadronische Materie ohne starke Wechselwirkung verlassen und so zur Messung der invarianten Masse des zerfallenen Mesons genutzt werden.

Die invariante Masse des Mesons ist gleich der Norm des Viererimpulses:

$$m_{inv} = \left\| \overrightarrow{P_{\rho}} \right\| = \left\| \left( \begin{array}{c} \overrightarrow{p}_{e^{+}} + \overrightarrow{p}_{e^{-}} \\ E_{e^{+}} + E_{e^{-}} \end{array} \right) \right\|$$

(1.1)

Wegen des hohen Impulses  $p_{e^{\pm}} \approx 100\,\mathrm{MeV}/c$  kann die Ruhemasse des Elektrons bzw. Positrons von  $m_{e^{\pm}} = 511\,\mathrm{keV}$  vernachlässigt werden. Es ergibt sich näherungsweise:

$$m_{inv} \approx 2 \cdot \sin\left(\frac{\alpha}{2}\right) \cdot \sqrt{p_{e^+} \cdot p_{e^-}}$$

(1.2)

Dabei bedeutet  $p_{e^{\pm}}$  den Impulsbetrag des Elektrons bzw. Positrons und  $\alpha$  den Winkel zwischen den beiden Impulsvektoren.

Durch Messung der Impulse und des Zwischenwinkels kann man die Massen der im Feuerball zerfallenden Mesonen spektroskopieren. Das neue HADES Spektrometer ist dafür ausgelegt, derartige Elektron-Positron-Paare mit großem Raumwinkel, hoher Massenauf"—lösung und sehr guter Untergrundunterdrückung zu messen.

### 1.2 Aufbau und Anforderungen des HADES Spektrometers

Als besondere Herausforderung an den Meßaufbau erweisen sich die geplanten Schwerionenstöße: so erwartet man bei zentralen Au-Au-Stößen im Mittel die Entstehung von bis zu 200 geladenen hadronischen Teilchen, die überwiegend in Vorwärtsrichtung, d.h. in die hinter dem festen Target gelegene Hemisphäre emittiert werden. Da aber nur in einem geringen Teil der zentralen Stöße auch wirklich ein  $\rho$ -Meson gebildet wird und außerdem der dileptonische Zerfallskanal stark unterdrückt ist, muß durch geeignete Maßnahmen die Nachweiswahrscheinlichkeit für Dileptonen maximal gehalten und eine effektive Unterdrückung des hadronischen Untergrundes (hauptsächlich p,  $\pi^+$  und  $\pi^-$ ) erreicht werden.

Abbildung 1.1: Schnitt durch das Dileptonenspektrometer HADES. Das Spektrometer ist rotationssymmetrisch zur Strahlachse aufgebaut, wobei jedes Detektorsystem aus sechs Teilstücken besteht. Die Magnetspulen erzeugen nur im Bereich zwischen inneren (MDC 1,2) und äußeren Driftkammern (MDC 3,4) ein Feld.

Im folgenden wird anhand von Abbildung 1.1 auf die grundlegende Struktur des Experimentaufbaus von HADES eingegangen, soweit dies zum Verständnis des Auslesekonzepts notwendig ist. Eine ausführliche Beschreibung des Spektrometers sowie der darin verwendeten Detektoren ist im HADES-Proposal [11] zu finden.

Rings um das segmentierte Target befindet sich ein Ringabbildender Čerenkov-Zähler (RICH), dessen Aufgabe die Leptonenidentifizierung von durchlaufenden Teilchen ist. Auf

die Funktionsweise des RICH wird in Abschnitt 1.3 näher eingegangen. Als nächstes Detektorsystem bilden vier Module von Vieldraht-Driftkammern (MDC) zusammen mit einem Magneten [2] aus sechs supraleitenden Spulen ein Magnetspektrometer, das Informationen über den Impuls der geladenen Teilchen liefert. Es werden die Spuren der Teilchen vor und nach dem Magnetfeld gemessen; aus der Ablenkung erhält man bei bekanntem Magnetfeld den Impuls des gemessenen Teilchens.

Den Abschluß des Spektrometers bildet ein Leptonen-Identifikationssystem, bestehend aus der Flugzeitwand sowie dem Preshower-Zähler. Geladene Teilchen, die unter Polarwinkeln größer  $45^{\circ}$  aus dem Target laufen, werden in der TOF-Wand über die Flugzeit identifiziert: Elektronen bewegen sich schneller als die schweren  $\pi$ -Mesonen und Protonen.

Teilchen, die unter Polarwinkeln kleiner 45° gestreut werden, können in der TOF-Wand nicht mehr eindeutig identifiziert werden, da die Flugzeitunterschiede zwischen Elektronen und den relativistischen Pionen zu klein werden. Zur Leptonenidentifikation benutzt man einen Preshower-Zähler, der aus drei Drahtkammern mit dazwischen liegenden Bleikonvertern besteht. Ausgenutzt wird hierbei, daß die in den Bleikonvertern von den Leptonen abgegebene Bremsstrahlung im Feld der Atomkerne in einen Schauer von Elektron-Positron-Paaren konvertiert und in den Drahtkammern nachgewiesen wird. Bei Hadronen findet diese Schauerbildung in wesentlich geringerem Umfang statt, eine Unterscheidung in Lepton und Hadron ist somit möglich.

Zusätzlich läßt sich aus der Gesamtanzahl der Treffer im TOF-Detektor auf die Pionenund Protonen-Multiplizität des betrachteten Ereignisses schließen; dies wird zur Erzeugung eines Multiplizitätstriggers für das Detektorsystem genutzt. Bei Schwerionenstößen kann somit zwischen peripheren (kleine Multiplizität) und zentralen Stößen (hohe Multiplizität) unterschieden werden.

### 1.3 Der RICH-Detektor

In Čerenkov-Zählern nutzt man die Tatsache aus, daß Teilchen, die sich mit Geschwindigkeiten  $v>v_P$  in einem Medium mit einem Brechungsindex n>1 bewegen, eine kegelförmige elektromagnetische Welle erzeugen. Die Phasengeschwindigkeit  $v_P$  des Lichtes ist im Medium definiert als

$$v_P = \frac{c_0}{n} \tag{1.3}$$

wobei  $c_0$  die Vakuumlichtgeschwindigkeit und n der Brechungsindex des betrachteten Mediums ist. Bewegt sich nun ein relativistisches Teilchen mit der Geschwindigkeit  $v>v_P$  im Medium, so wird in Vorwärtsrichtung unter dem Winkel  $\theta_C$  elektromagnetische Strahlung abgegeben:

$$\cos \theta_C = \frac{c}{v} = \frac{c_0}{n \cdot v} \le 1 \tag{1.4}$$

Gibt man nun ein Material mit einem bestimmten Brechungsindex n vor, so können nur Teilchen mit Geschwindigkeiten  $v \geq c_0/n$  in diesem Medium Čerenkov-Licht erzeugen. Der Öffnungswinkel  $\theta_C$  ist dabei ein Maß für die Geschwindigkeit des Teilchens.

Bei HADES wird der Čerenkov-Effekt ausgenutzt, um die emittierten relativistischen Elektronen bzw. Positronen  $(v/c \approx 1)$  von den deutlich langsameren Hadronen  $(v/c \approx 0.95)$  zu unterscheiden. In der von HADES verwendeten Geometrie ist ein Aufbau der lichtempfindlichen Detektoren in Strahlrichtung nicht möglich. Abhilfe schafft das Konzept des Ringabbildenden Čerenkov-Zählers: das entstehende Licht wird über einen Spiegel in die Hemisphäre hinter dem Target geworfen und dort nachgewiesen. Die abbildenden Eigenschaften des Spiegels bewirken eine Fokussierung des Čerenkov-Lichts in die Detektorebene; der Lichtkegel wird als Čerenkov-Ring abgebildet.

Die Information über die Teilchengeschwindigkeit steckt im Durchmesser des Rings; die Geschwindigkeitsmessung wird damit auf eine Ortsmessung reduziert. Bei HADES erwartet man, daß sich fast alle zu detektierenden Leptonen mit annähernd gleicher Geschwindigkeit  $v \approx c$  [9] bewegen. Daher variiert der Ringdurchmesser nur unwesentlich, was eine anschließende Ringerkennung (die wegen der höheren Verarbeitungsgeschwindigkeit in Hardware implementiert ist) wesentlich erleichtert.

Abbildung 1.2: Schnitt durch den HADES RICH. Der Photonendetektor besteht aus einer Vieldrahtproportionalkammer mit CsI-Photokathode. Im Detailbild erkennt man die Segmentierung der Kathodenebene zum Erreichen der benötigten hohen Ortsauflösung. Die Ankoppelung der Ausleseelektronik erfolgt über die ebenfalls dargestellten Steckverbinder.

Der Aufbau des HADES RICH ist als Querschnitt in Abbildung 1.2 gezeigt. Der Detektor besteht aus zwei durch eine  $CaF_2$ -Scheibe getrennten Gasvolumen. Das in Strahlrichtung gelegene Volumen dient als Radiator. Es ist mit  $C_4F_{10}$  (Brechungsindex  $n \approx 1,004$  [11]) gefüllt und enthält außerdem den aus mehreren Segmenten zusammengesetzten Spiegel. Aufgrund der verwendeten Geometrie (das Target liegt in Strahlrichtung hinter der  $CaF_2$ -

Trennscheibe) und der Stoßkinematik gelangen fast alle im Stoß entstehenden Teilchen direkt in das Radiatorgasvolumen; in seltenen Fällen können die geladenen Teilchen jedoch auch direkt in das Zählergas gelangen. Das Radiatorgas ist so gewählt, daß nur geladene Teilchen mit Geschwindigkeiten  $v > 0.99\,c$  [11] Čerenkov-Licht aussenden können, nicht jedoch Teilchen mit kleineren Geschwindigkeiten. Das Radiatorgas ist somit hadronenblind und nur auf Elektronen und Positronen empfindlich.

Da die im Schwerionenstoß entstehenden Teilchen in die hinter dem RICH positionierten Detektorsysteme gelangen sollen, mußten für die Konstruktion des Spiegels und der Druckschale, die das Radiatorgasvolumen strahlabwärts abschließt, Lösungen mit großer Strahlungslänge gewählt werden. Details zu diesen Komponenten finden sich in [15]. Das entstehende Licht wird über den Spiegel in das rückwärtig gelegene Zählervolumen gelenkt. Dabei muß es die Trennscheibe passieren, für die wegen der benötigen hohen Transmission im VUV-Bereich ( $\lambda \approx 140 \, \mathrm{nm}$ ) Kalziumfluorid als Material gewählt wurde.

Das Zählervolumen bildet zusammen mit den eigentlichen Detektormodulen einen Vieldraht-Proportionalzähler zum Nachweis der im Radiatorvolumen erzeugten Čerenkov-Photonen. Da man pro Lepton den Simulationen nach nur mit einer sehr geringen Anzahl von etwa 12 – 20 Photonen [31] pro Ring rechnen kann, ist der Zähler auf den Nachweis von einzelnen Photonen ausgelegt. Die Čerenkov-Photonen durchlaufen das Zählergas (CH<sub>4</sub>, hohe Transmission im VUV-Bereich) und treffen auf eine speziell beschichtete Kathodenebene, die die Photokathode des Zählers bildet. Sie ist pro Sektor aus 4712 einzelnen, mit einer Schicht aus Graphit und Cäsiumiodid (CsI) versehenen Elementen (den Pads), aufgebaut. Beim Auftreffen auf ein Pad löst ein Čerenkov-Photon mit im Mittel 20% Wahrscheinlichkeit (Quanteneffizienz) ein Photoelektron aus, das nach der Gasverstärkung im  $CH_4$  (ca.  $10^5$ ) als Influenzladung auf dem Pad nachgewiesen werden kann. Sollten geladene Teilchen in den Photonendetektor gelangen, so würde dies im allgemeinen zu einer deutlich höheren Ladungsmenge und damit Pulshöhe führen. Somit kann über die Pulshöhe in der Off"—line-Analyse eine Unterscheidung zwischen Photonen und geladenen Teilchen durchgeführt werden. Hierbei wird auch ausgenutzt, daß die Teilchen charakteristische Signaturen im Detektor hinterlassen: Leptonen bilden einen Ring mit mittleren Pulshöhen, geladene Hadronen je nach Eintrittswinkel einen Strich oder einen Fleck mit hohen Pulshöhen.

Im Rahmen der vorliegenden Arbeit wurde die Signalauslese und die digitale Weiterverarbeitung der Daten des RICH Detektors bis hin zur Datenaufnahme zur Einsatzreife gebracht. In den folgenden Kapiteln werden nach dem HADES Auslese- und Triggerkonzept die Details des RICH-Auslesesystems beschrieben und über erste Erfahrungen im Laborbetrieb berichtet.

Da sich bei der Beschreibung des Auslesesystems fachspezifische Ausdrücke und in der Kollaboration häufig benutzte Abkürzungen nicht vermeiden lassen, ist am Ende der Arbeit ein Glossar (ab Seite 91) angefügt, das diese Begriffe jeweils kurz erläutert. Aus Gründen der Übersichtlichkeit wurde auf die Erklärung der Begriffe direkt im Text verzichtet.

## Kapitel 2

# Das HADES Auslese- und Triggerkonzept

Das HADES Spektrometer ist nicht nur als Instrument höchster Auf"—lösung und Akzeptanz konzipiert, sondern auch für hohe Ereignisraten ausgelegt, die eine optimale Nutzung des vom SIS-Beschleuniger verfügbaren Strahlstroms (bis zu  $10^8$  Au-Ionen pro Sekunde) ermöglicht [11]. Im Mittel erwartet man für ein Target mit 1% Wechselwirkungsdicke  $10^6$  Kernreaktionen pro Sekunde, wovon erfahrungsgemäß etwa 10% ausreichend zentral ablaufen. Die Ausleseelektronik muß daher in der Lage sein, eine Rate von bis zu  $10^5$  Ereignissen pro Sekunde zu verarbeiten. Aufgrund der hohen Pionen- und  $\gamma$ -Multiplizität ( $\pi^0 \to \gamma\gamma$ ) und trotz der großen Strahlungslänge von Target und Detektorsystem wird pro zentralem Stoß etwa ein Elektron aus externer Konversion erwartet. Dagegen sind die interessanten  $e^+$ - $e^-$ -Paare aus Mesonenzerfällen um einen Faktor  $10^4$  –  $10^5$  unterdrückt.

Die Rate von  $10^5$  beschränkt die maximal erlaubte Totzeit des Detektors auf  $10\mu$ s. Betrachtet man beispielsweise den RICH, der pro Sektor 4712 auszulesende Pads besitzt, und vernachlässigt sämtliche zur Verwaltung der Daten notwendigen Zusatzinformationen, so ergibt sich bei einer Rate von  $10^5$  Hz eine auszulesende Roh-Datenmenge von

$$10^5 \frac{1}{s} \cdot 6 \text{ Sektoren} \cdot 4712 \frac{\text{Pads}}{\text{Sektor}} \cdot 16 \frac{\text{Bits}}{\text{Pads}} \approx 5,27 \text{ Gigabyte/s}$$

(2.1)

Dies ist eine Datenmenge, die mit keinem heute kommerziell erhältlichen System zu verarbeiten ist. Auch die Speicherung der Daten wäre bei den Strahlzeiten, die jeweils mehrere Wochen dauern, nicht durchführbar.

Für HADES wurde deshalb ein mehrstufiges Auslesesystem entworfen, das folgenden Ansprüchen gerecht werden soll [17]:

- 1. Hohe Ratenfestigkeit bis zu  $10^5$  Hz

- 2. Erfassung und Speicherung nur von physikalisch interessanten Ereignissen

- 3. Eindeutige Zuordnung von Daten zu einem Ereignis

- 4. Leichte Anpaßbarkeit an die verwendeten verschiedenen Detektorsysteme

Dieses Trigger- und Auslesekonzept soll im folgenden kurz vorgestellt werden.

### 2.1 Das Triggersystem

Im Gegensatz zu früheren Experimenten wird bei HADES ein neues, asynchron arbeitendes mehrstufiges Auslesesystem verwendet. Bei einem synchronen System wird mit einem gemeinsamen Triggersignal die Datenaufnahme gestartet und anschließend das gesamte Detektorsystem ausgelesen; nach jedem Trigger erhält man sofort einen kompletten Datensatz. Das langsamste Detektor-Auslesesystem bestimmt die Totzeit des Gesamtsystems. Die oben beschriebenen Anforderungen erfordern jedoch ein neues Konzept: der Datenweg vom Detektor zum Speichersystem wird in mehrere asynchron arbeitende Pufferstufen zerlegt. So kann das Triggersignal zur schnellen Speicherung in der ersten Pufferstufe genutzt und damit eine kurze Totzeit erreicht werden; ein mehrstufiges Triggersystem koordiniert den Weitertransport der Daten zu weiteren Pufferstufen und ermöglicht eine Selektierung von interessanten Datensätzen. Den Daten hinzugefügte Verwaltungsinformationen ermöglichen anschließend das Zusammensetzen der zu speichernden Datenpakete zu einem kompletten Ereignis.

Eine ausführliche Erläuterung zum HADES-Triggerkonzept findet man in [21], hier wird nur eine kurze Übersicht über die einzelnen Triggerstufen gegeben.

#### Der LVL1-Trigger (Multiplizität)

Der LVL1-Trigger wird aus den Daten von TOF bei einer für einen zentralen Stoß hinreichend großen Multiplizität erzeugt. Er bewirkt die Erfassung der in den einzelnen Detektorsystemen anstehenden analogen Daten sowie deren digitale Speicherung in der ersten Pufferstufe (der LVL1-Pipe). Außerdem werden die so erfaßten Daten der zur Entscheidungsfindung verwendeten Detektoren an entsprechende Bildverarbeitungs- und Entscheidungseinheiten weitergeleitet.

#### Der LVL2-Trigger (Leptonenpaare)

Aus den Ergebnissen der Bildverarbeitungssysteme wird in einer Entscheidungseinheit der LVL2-Trigger gewonnen. Die wesentlichen Entscheidungskriterien für den Nachweis eines Leptons sind: Ringerkennung im RICH, Schauererkennung im PreShower oder geeignete Flugzeit im TOF. Bei ausreichenden Hinweisen auf ein für die betrachtete Physik interessantes Ereignis werden über den LVL2-Trigger die jeweiligen Datensätze in die zweite Pufferstufe (die LVL2-Pipe) übertragen, andernfalls werden die Datensätze direkt in der LVL1-Pipe gelöscht.

2.2. DIE LVL1-PIPE 9

Die Kombination aus LVL1- und LVL2-Trigger sorgt also dafür, nur potentiell relevante Datensätze zu erzeugen und zu transportieren, die ein  $e^+$ - $e^-$ -Paar enthalten. Wegen der notwendigen Geschwindigkeit sind die Bewertungssysteme komplett in Hardware aufgebaut. Eine weitere Siebung der Datensätze ist notwendig, da stets ein gewisser Anteil von falschen Entscheidungen getroffen wird: einerseits erlaubt die Realisierung der Mustererkennung in Hardware nur relativ einfache Algorithmen, andererseits können bei unvollständigem Nachweis von Teilchen in den Detektorsystemen falsche Identifizierungen entstehen.

#### Der LVL3-Trigger (Teilchenspur-Analyse)

Die letzte Triggerstufe ist komplett in Software realisiert. Die Ergebnisse der Teilchenspur-Analyse der MDC-Daten werden mit den Ringmittelpunkten aus der Entscheidungseinheit verglichen und bei entsprechender Übereinstimmung der LVL3-Trigger erzeugt. Mit diesem Trigger werden die CPUs angewiesen, bestimmte Datensätze aus den LVL2-Pipes über ein ATM-Netzwerk zu einem zentralen Server zu transportieren, dort zu einem kompletten Datensatz zusammenzusetzen und zur späteren Analyse auf Magnetband zu speichern. Diese Triggerstufe dient im wesentlichen zur Unterdrückung von Untergrundereignissen und Fehlzuordnungen von  $e^+$ - $e^-$ -Paaren.

### 2.2 Die LVL1-Pipe

Die LVL1-Pipe bildet die erste Pufferstufe des Auslesesystems. In ihr werden auf einen LVL1-Trigger hin die Daten der einzelnen Detektoren bis zur Entscheidung über ihre weitere Verwendung zwischengespeichert. In der LVL1-Pipe befinden sich daher Detektordaten für alle Ereignisse mit und ohne Leptonengehalt. Da das Triggersystem eine bestimmte Zeit (bei HADES rechnet man mit 200 – 400  $\mu$ s [20]) zur Erzeugung des LVL2-Triggers benötigt, ist die LVL1-Pipe auf die Speicherung mehrerer kompletter Datensätze ausgelegt. Die Pufferfunktion erfordert außerdem die Möglichkeit des vollkommen asynchronen Schreib- und Lesezugriffs auf die LVL1-Pipe.

Bei HADES ist das Augenmerk auf zentrale Schwerionenstöße gerichtet. Die resultierende hohe Multiplizität an geladenen Teilchen bedeutet für alle Detektoren, die nicht hadronenblind wie der RICH sind, eine hohe Belegungsmultiplizität der Detektorzellen. Die Speichergröße der LVL1-Pipe ist daher durch die Segmentierung der einzelnen Detektoren bedingt und beispielsweise beim RICH ausgelegt zur Speicherung von 120 Ereignissen (siehe Abschnitt 3.1).

Datensätze, die die Signatur eines Leptonenpaares nicht enthalten, können noch vor dem Transport verworfen werden. Das im Vergleich zum Transport der Daten erheblich schnellere Löschen in der LVL1-Pipe verhindert das Voll-Laufen der LVL1-Pipe und ermöglicht eine effektive Nutzung der Pufferstruktur in der Datenaufnahme.

### 2.3 Die LVL2-Pipe

Die zweite Pufferstufe des HADES Auslesesystems wird als LVL2-Pipe bezeichnet. Im Gegensatz zur LVL1-Pipe stehen in der LVL2-Pipe nur noch Datensätze, die Signaturen für ein Dilepton-Ereignis aufweisen. Eine weitere Besonderheit ist, daß alle Datensätze in der LVL2-Pipe bereits so formatiert sind, daß beim weiteren Transport keinerlei Softwareeingriffe in die Datensätze notwendig sind. Diese Formatierung ermöglicht erst den schnellen Transport von Daten aus der LVL2-Pipe zur Speicherung in der DAQ.

Die LVL2-Pipe wird über den LVL2-Trigger mit Datensätzen aus der LVL1-Pipe gefüllt. Man erwartet bei der vorgesehenen Erzeugung des LVL2-Triggers an dieser Stelle eine Reduktion der zu transportierenden Daten um den Faktor 100. Dies reduziert die Anforderungen an die Bandbreite des Auslesesystems.

Die LVL2-Pipe stellt außerdem die eigentliche Schnittstelle zur DAQ-Software dar.

### 2.4 Speicherung in der DAQ

Als letzte Stufe des Auslesesystems steht die Speicherung der Datensätze in der Datenaufnahme (data aquisition, DAQ). Hierbei wird nochmals über den LVL3-Trigger eine Selektierung der Datensätze vorgenommen. Durch die in den ersten zwei Stufen vorgenommene Datenreduktion ist dies zeitlich unkritisch, die maximal erlaubte Zeit zur Bearbeitung eines Datensatzes hat deutlich zugenommen.

Bei HADES werden kommerzielle Systeme zur Speicherung der Daten eingesetzt. Die in den LVL2-Pipes der einzelnen Detektoren gepufferten Datensätze werden auf Anweisung des LVL3-Triggers hin über ein schnelles ATM-Netzwerk auf einem zentralen Server gesammelt und dort vom Eventbuilder zu kompletten Ereignissen zusammengesetzt. Im Gegensatz zu synchronen Auslesesystemen entstehen diese Datensätze erst mit Verzögerung, die durch das mehrstufige Triggersystem bedingt sind. Beim Zusammensetzen der Ereignisse muß auch auf das asynchrone Verhalten des Auslesesystems Rücksicht genommen werden: Daten einzelner Detektoren können mit Verspätung relativ zueinander eintreffen; vor der Speicherung steht deshalb wiederum eine Pufferstufe, die diese Verzögerungen ausgleicht.

# Kapitel 3

# Das RICH Auslesesystem

### 3.1 Erwartete Datenmengen

Im gesamten RICH-Detektor befinden sich insgesamt 28 272 ladungsempfindliche Pads, deren Pulshöhen zusammen mit der Koordinate des entsprechenden Pads gespeichert werden müssen (siehe Formel 2.1). Um die notwendige Datenrate bei der Auslese der Analogdaten zu reduzieren, ist es sinnvoll, unter Beachtung der Randbedingungen die Auslese des Detektors zu parallelisieren:

- 1. Eine obere Grenze für die Auslese wird durch die maximale Totzeit von  $10\mu$ s vorgegeben. Innerhalb dieser Zeit ist es nur möglich, eine bestimmte Anzahl an Analogdaten zu digitalisieren und zu speichern.

- 2. Zur Reduktion der Datenmenge sollten nur Pulshöhen gespeichert werden, die von Photonen stammen, nicht jedoch das stets vorhandene Rauschen des Systems.

- 3. Die verwendeten Komponenten des Systems geben eine maximale Taktfrequenz von ca. 32 MHz vor, die prinzipiell nicht überschritten werden kann.

- 4. Der Anteil an Verwaltungsinformationen sollte in vernünftigem Verhältnis (etwa 10%) zu den Nutzdaten stehen.

Diese Randbedingungen haben beim RICH zur Entscheidung geführt, jeweils Gruppen von 64 Pads (im folgenden auch Kanäle genannt), parallel auszulesen. Diese Aufteilung reduziert einerseits die Datenmenge, die pro Gruppe in der erlaubten Zeit erzeugt wird (und damit die benötigte Bandbreite). Andererseits müssen Verwaltungsinformationen hinzugefügt werden, die beim späteren Zusammenführen der Daten eine eindeutige Zuteilung von Pulshöhen zu den Kanälen erlauben.

Der Detektor ist in 6 Sektoren mit jeweils 4712 Pads aufgeteilt. Bei einer Aufteilung jedes Sektors in Gruppen zu 64 Kanälen ergibt sich die Anzahl der für einen Sektor mindestens notwendigen Auslesegruppen zu

$$4712 \operatorname{Pads} \cdot \left(64 \frac{\operatorname{Pads}}{\operatorname{Auslesegruppe}}\right)^{-1} = 74 \operatorname{Auslesegruppen}$$

(3.1)

Aus technischen Gründen bei der Produktion des Detektors werden pro Sektor allerdings 75 Auslesegruppen benötigt; für den gesamten Detektor sind also  $6 \cdot 75 = 450$  Auslesegruppen notwendig.

Um innerhalb einer Auslesegruppe einen Kanal eindeutig zu identifizieren, wird der Pulshöhe (die mit 10bit Auf"—lösung gespeichert wird) eine in 6bit kodierte Kanalnummer zugeordnet. Jeder Datensatz wird außerdem mit einer Nummer (dem sog. Triggertag) abgespeichert, die für alle Datensätze eines Ereignisses gleich ist und somit später eine eindeutige Zusammenführung von einzelnen Datensätzen erlaubt. Pro Auslesegruppe ergibt sich somit bei der angepeilten LVL1-Triggerrate von  $10^5$  Hz eine Datenrate pro Auslesegruppe von:

$$10^{5} \frac{1}{s} \cdot \left(64 \operatorname{Pads} \cdot 16 \frac{\operatorname{bit}}{\operatorname{Pad}} + 16 \operatorname{bit}\right) = 12,4 \operatorname{Megabyte/s}$$

(3.2)

In dieser Formel ist die maximale Anzahl von 64 Kanälen und die Verwaltungsnummer berücksichtigt. Die Datenrate ist mit den verwendeten Komponenten zu bewältigen. Jedoch hat sich — bedingt durch das Einfügen von Verwaltungsinformationen — das Datenaufkommen bezogen auf den gesamten Detektor auf 5,4 Gigabyte/s erhöht.

Eine weitere Reduktion der Datenmenge, die in der LVL1-Pipe zu speichern ist, erreicht man, wenn man das elektronische Rauschen der nicht getroffenen Kanäle effektiv unterdrückt. Somit werden nur die Daten von wirklich getroffenen Pads gespeichert. Aus Simulationen und ersten Experimenten mit dem Prototypzähler erwartet man, daß pro Ereignis maximal 10% aller Pads wirklich ansprechen. Im Schnitt reduziert das bei homogen angenommenem Ansprechen des Detektors die Datenrate pro Auslesegruppe auf:

$$10^{5} \frac{1}{s} \cdot \left(64 \operatorname{Pads} \cdot 10\% \cdot 16 \frac{\operatorname{bit}}{\operatorname{Pad}} + 16 \operatorname{bit}\right) = 1,4 \operatorname{Megabyte/s}$$

(3.3)

Weitere Anforderungen entstehen durch das in Abschnitt 2.1 erläuterte mehrstufige Triggersystem. Es ist notwendig, an zwei Stellen Zwischenspeicher einzufügen, die jeweils mehrere Datensätze bis zur weiteren Verarbeitung speichern können. Dabei ergibt sich aus der Geschwindigkeit der Einheit, die über die weitere Verwendung der Daten entscheidet, die jeweils notwendige Tiefe des Zwischenspeichers:

• Bei der LVL1-Pipe bestimmt die Verzögerung durch die Bildverarbeitungs- und Entscheidungseinheit die notwendige Tiefe. Man rechnet mit einer Durchlauf"—latenz von etwa 40 Ereignissen [20] bis zur Erzeugung des LVL2-Triggers. Bezogen auf die durchschnittliche Ereignisgröße (siehe Formel 3.3) ergibt sich die Tiefe der LVL1-Pipe zu

$$40 \cdot 10\mu \text{s} \cdot 10^5 \frac{1}{\text{s}} \cdot \left(64 \text{ Pads} \cdot 10\% \cdot 16 \frac{\text{bit}}{\text{Pad}} + 16 \text{ bit}\right) \cdot \frac{1}{16} \frac{1}{\text{bit}} = 296 \text{ Worte}$$

(3.4)

Aus Sicherheitsgründen wurde die LVL1-Pipe des RICH deutlich größer ausgelegt: die Speichertiefe von 1024 Worte (entsprechend 128 durchschnittlichen Ereignissen) liegt um den Faktor 3 über dieser Abschätzung und ermöglicht selbst im unwahrscheinlichsten Fall (Ansprechen des gesamten Detektors) das Zwischenspeichern von 15 Ereignissen.

• Für die Tiefe der LVL2-Pipe entscheidend ist die Verarbeitungsgeschwindigkeit des Spurerkennungsalgorithmus auf der CPU. Diese ist jedoch nur schwer abschätzbar, da sich diese Algorithmen noch in der Entwicklung befinden; außerdem lassen sich sowohl durch Softwareoptimierung als auch durch die stetig voranschreitende Entwicklung auf dem Gebiet der Rechnertechnik Geschwindigkeitsoptimierungen vornehmen. Für die verwendete Ausleseelektronik wurde ein Speicher von 512 kByte vorgesehen. Die hierfür notwendige Abschätzung setzt jedoch Kenntnisse über den internen Aufbau des Auslesesystems voraus und wird deshalb erst in Abschnitt 5.6 gebracht.

### 3.2 Weitere Anforderungen

Das Auslesesystem muß in der Lage sein, die Daten aus der LVL1-Pipe mit hoher Geschwindigkeit und in der für das weiterverarbeitende System korrekten Form zu übertragen. Hierbei ist es wünschenswert, daß eine beliebige Transformation der jeweiligen Padkoordinaten erfolgen kann. Dies erleichtert sowohl die Entwicklung des Bildverarbeitungssystems und des Frontends als auch einen später eventuell notwendigen Wechsel zu einem System mit anderen Anforderungen.

Für das RICH Auslesesystem ergeben sich also folgende weitere Anforderungen:

- 5. Leichte Skalierbarkeit

- 6. Hohe Verarbeitungsgeschwindigkeit

- 7. Wartungsfreundlichkeit des Gesamtsystems

Um diese Anforderungen zu erfüllen, wurde das Auslesesystem in mehrere Module aufgeteilt: Die eigentliche Datenaufnahme und Zwischenspeicherung in der LVL1-Pipe findet direkt am Detektor im Frontend-Modul (entspricht einer Auslesegruppe) statt. Die Zusammenfassung der einzelnen Datensätze aus den LVL1-Pipes des RICH findet im Readout-Controller statt. Dieses Modul steuert über ein einfaches Interface die Auslese von Daten aus bis zu 64 Frontend-Modulen und deren Speicherung in der LVL2-Pipe. Als Schnittstelle zur zentralen Triggereinheit dient die Detektor-Triggereinheit (DTU), die die Umsetzung der einzelnen Triggerbefehle in Auslesezyklen vornimmt.

Diese Modularisierung ermöglicht eine leichte Erweiterung des Systems bei neu hinzukommenden Detektormodulen und erhöht die Verarbeitungsgeschwindigkeit des Auslesesystems durch die hohe Parallelisierung der Datenerfassung in den Frontend-Modulen. Der Austausch defekter Module wird ebenfalls erleichtert.

Die Aufteilung des RICH Auslesesystems in drei Module stellt somit einen guten Kompromiß dar: der Verkabelungsaufwand am Detektor hält sich in Grenzen, die Übersichtlichkeit des Gesamtsystems bleibt erhalten.

### 3.3 Einbindung in das HADES-Triggerkonzept

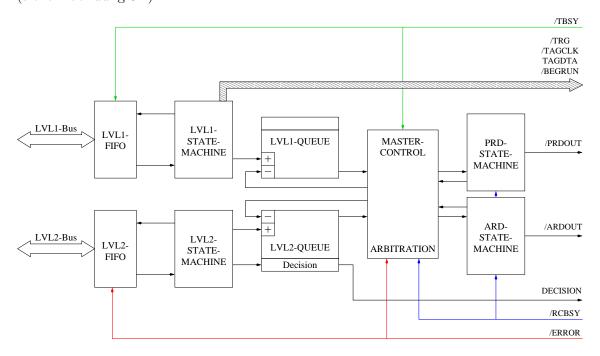

Die Umsetzung der in Kapitel 2 vorgestellten Anforderungen an das Auslesesystem und dessen Einbindung in das Triggerkonzept werden hier schematisch anhand Abbildung 3.1 dargestellt.

Abbildung 3.1: Auslese- und Triggersystem für den HADES RICH. Die üblicherweise verwendeten Abkürzungen für einige Komponenten sind ebenfalls angegeben (genaue Bedeutung siehe Glossar).

Die Erzeugung des Triggersignals läuft wie folgt ab: Aus der vom TOF-Detektor gelieferten Multiplizität wird ein Triggersignal erzeugt und in die Triggereinheit geleitet. Ist das System momentan aufnahmebereit, so wird dieser Multiplizitätstrigger in einen LVL1-Trigger umgesetzt, der an alle angeschlossenen Detektoreinheiten verteilt wird.

Beim RICH löst dieser LVL1-Trigger folgende Funktionen aus:

- Analoge Signalverarbeitung

- Analog-Digital-Wandlung der Pulshöhen

- Vergleich mit den vorgegebenen Schwellwerten

- Abspeichern in der LVL1-Pipe

Anschließend werden die Daten an die Bildverarbeitungseinheit weitergeleitet. Diese sucht in den Daten nach Ringsignaturen und leitet die Koordinaten der gefundenen potentiellen Ringmittelpunkte an die Entscheidungseinheit weiter. Dort werden diese Daten mit den aus TOF und Preshower gelieferten Koordinaten von möglichen Leptonenkandidaten verglichen. Bei genügend hoher Übereinstimmung der Teilchenkoordinaten wird über die Triggereinheit ein LVL2-Trigger mit positiver Entscheidung ausgegeben. Dies führt dazu, daß die Daten aus der LVL1-Pipe in die LVL2-Pipe übertragen werden. Sollte keine ausreichende Übereinstimmung zwischen RICH- und TOF- bzw. Preshower-Daten vorliegen, so werden die in der LVL1-Pipe zwischengespeicherten Daten per LVL2-Trigger mit negativer Entscheidung gelöscht.

Während der Zeit, in der die Bildverarbeitungs- und die Entscheidungseinheit die einlaufenden Daten untersuchen, können bereits neue LVL1-Trigger von der Triggereinheit erzeugt werden. Diese Daten werden zwischengespeichert und — sobald die weiterverarbeitenden Einheiten wieder empfangsbereit sind — an diese weitergeleitet.

Anschließend werden die Ansprechmuster (hit pattern) von MDC, TOF, Preshower und RICH durch einen Spurerkennungsalgorithmus verglichen. Bei Übereinstimmung der Ergebnisse wird ein LVL3-Trigger erzeugt und die ausgewählten Datensätze aus der LVL2-Pipe über ein ATM-Netzwerk an die Datenspeichereinheit übertragen.

Auch hier können während der Bearbeitung der in der LVL2-Pipe anstehenden Daten neue hinzukommen.

### 3.4 Technische Realisierung

In Abbildung 3.1 wurde bereits eine gewisse Aufteilung nach Funktionsblöcken vorgenommen. Für die technische Realisierung gibt es jedoch noch einige Randbedingungen, die eine weitere Unterteilung in einzelne Baugruppen erforderlich machen.

- Der Photonendetektor des RICH ist in sechs gleich aufgebaute Sektoren unterteilt. Jeder dieser Sektoren beinhaltet 75 Auslesegruppen, die in jeweils einem Frontend-Modul verwirklicht werden.

- Um eine möglichst hohe Auslesegeschwindigkeit bei geringem Verkabelungsaufwand zu erreichen, werden jeweils 5 Frontendmodule auf einer Treiberplatine (backplane) verkettet (daisy chaining). Pro Sektor erhält man damit 16 Ketten von Frontendmodulen.

- Diese Ketten müssen in sinnvollen Gruppen zusammengefaßt werden. Da der hierfür verwendete Readout-Controller auf dem VME-Bus basieren soll und somit die nutzbare Platinenfläche festgelegten Begrenzungen unterliegt, werden jeweils 8 Frontendketten an die Eingänge (ports) eines Readout-Controllers angeschlossen. Zusätzlich erzielt man auch in dieser Stufe durch die Parallelisierung des Ausleseprozesses Geschwindigkeitsgewinne.

Die Auslese der in den Readout-Controllern implementierten LVL2-Pipe erfolgt durch VME-CPUs, die jeweils die Readout-Controller von zwei Sektoren in einem VME-Crate ansteuern. Diese Zusammenfassung kommt ebenfalls den Platzansprüchen der Ausleseelektronik entgegen, die wegen möglichst kurzer Kabellängen direkt hinter den Photonenzählermodulen im Experimentaufbau untergebracht ist.

Die Triggerverteilung ist aus praktischen Überlegungen ebenfalls in zwei Teile aufgespalten:

- Der zur Umsetzung des Multiplizitätstriggers notwendige Teil wird ebenso wie die Schnittstelle zur Bildverarbeitung (der IPU) auf einer zentralen Triggereinheit (der CTU) implementiert, die zentral für den gesamten Experimentaufbau Triggerbefehle erzeugt und über den Triggerbus an alle Detektorsysteme verteilt.

- Sämtliche zur Ansteuerung der jeweiligen Detektor-Ausleseelektronik notwendige Logik wird in sogenannte DTUs ausgelagert. Diese Baugruppe ist ebenfalls als VME-Karte ausgelegt und steuert beim RICH jeweils vier Readout-Controller an. Die DTU-Module sind für alle Detektorsysteme gleich ausgelegt und werden durch die Programmierung des steuernden FPGAs sowie eventuell notwendige Aufsteckmodule (z.B. zur Pegelwandlung) an die jeweiligen Detektoren angepaßt.

Der modulare Aufbau sowohl des Triggersystems als auch der Ausleseelektronik hat sich sowohl bei Labortests als auch bei den Elektroniktests im Rahmen von Teststrahlzeiten als sinnvoll erwiesen. So kann jede Gruppe mit einer Kombination aus CTU, DTU und der jeweiligen Ausleseelektronik getrennt ihre Systeme testen und anschließend das Auslesesystem durch Verbinden einer CTU mit den jeweiligen DTUs zu einem gemeinsamen Triggerbus erweitern.

In den Labortests der RICH-Ausleseelektronik wurde diese Skalierbarkeit ebenfalls ausgenutzt. Das System wurde Schritt für Schritt, ausgehend von einem Readout-Controller und einem Frontend, aufgebaut. Dabei auftretendes Fehlverhalten wurde in einem Minimalsystem reproduziert und somit einer systematischen Fehlersuche zugänglich gemacht. Als Ergebnis dieser Entwicklung konnte schon nach sechs Monaten der Schritt vom Prototypen zum endgültigen Serienmodell vorgenommen werden.

## 3.5 Auswahl der verwendeten Technologie

Zur Implementierung der benötigten Funktionen wurde anfangs eine Entscheidung über den Aufbau der Systemkomponenten getroffen. Dabei mußte ein Kompromiß zwischen den folgenden Anforderungen gefunden werden:

- 1. Flexibilität

- 2. Erweiterbarkeit

- 3. Geschwindigkeit

- 4. Kosten

Für das RICH-Auslesesystem wurde als Optimum eine Kombination aus Analog-ASICs, einigen Standardkomponenten und FPGAs ausgewählt. Zum besseren Verständnis dieser Wahl werden in den folgenden Abschnitten die zur Auswahl stehenden Technologien mit ihren Vor- und Nachteilen diskutiert.

#### 3.5.1 Standardkomponenten

Als Standardkomponenten bezeichnet man in der Elektronik Bauelemente und integrierte Schaltungen, die auf Grund ihrer weiten Verbreitung in der Industrie in großen Stückzahlen und zu günstigen Preisen erhältlich sind. Bedingt dadurch gibt es bereits viele Geräte, in denen diese Komponenten verwendet werden, was sich sowohl in ihrer Zuverlässigkeit als auch einer breiten Anzahl an Anwendungsbeispielen positiv niederschlägt.

Ein typisches Beispiel für Logik-Standardbausteine sind die ICs der Baureihe 74xx, die in verschiedenen Familien seit etlichen Jahren von mehreren Herstellern gefertigt werden und an bestimmte Anforderungen angepaßt sind. Ebenso sind Standardspeicher in nahezu beliebigen Größen, Konfigurationen und Technologien erhältlich.

Jedoch zeigt bereits eine grobe Abschätzung, daß ein Aufbau der Ausleseelektronik nur aus solchen Standardkomponenten scheitern muß:

- Die elf auf einem Readout-Controller untergebrachten FPGAs enthalten insgesamt das Äquivalent von ca. 49 000 Logikgattern.

- Typische ICs der 74xx-Reihe enthalten in einem 16poligen Gehäuse vier Logikgatter.

- Der Platzbedarf eines in SMT montierten Gehäuses samt minimal benötigter Verdrahtung beträgt etwa  $20 \cdot 10 \text{ mm}^2$ .

Somit würde z.B. im Readout-Controller alleine für die Steuerlogik ein Platzbedarf von

$$49\,000\,\text{Gatter} \cdot 0.25\,\frac{\text{IC}}{\text{Gatter}} \cdot 20 \cdot 10\,\frac{\text{mm}^2}{\text{IC}} = 2.45\,\text{m}^2 \tag{3.5}$$

entstehen, der aber auf einer VME-Buskarte nicht zur Verfügung steht.

Darüberhinaus wäre ein so aufgebautes System nicht flexibel genug; für jede Anderung in der Steuerlogik müßten Hardwareänderungen vorgenommen werden. Auch zeigen Überlegungen zum Stromverbrauch und der durch die vielen Verbindungen langen Signalwege, daß ein Aufbau des Systems aus Standardkomponenten nicht realisierbar ist.

Trotzdem wurden an einigen Stellen Standardkomponenten ins Auslesesystem integriert:

- Der VME-Bus-Chipsatz wurde als "off-the-shelf" 1-Lösung gewählt. Dies hat den Vorteil, daß man das Spezialwissen der jeweiligen Firma nutzen und auf eine eigene, fehlerträchtige Umsetzung des teilweise komplexen VME-Bus-Protokolls verzichten kann.

- Die Speicher der LVL1- und LVL2-Pipe sowie die zum Mapping benötigten Speicherbausteine wurden ebenfalls aus gängigen Komponenten realisiert.

- An bestimmten Stellen im System wurden auf spezielle Aufgabenbereiche zugeschnittene Standardkomponenten der 74xx-Reihe verwendet, so zum Beispiel Treiberbausteine zum Aufbereiten von Datensignalen für die Flachbandkabel.

#### 3.5.2 CPLDs

Wegen der mangelnden Flexibilität von Standard-Logikkomponenten wurden in der Industrie bereits vor einigen Jahren Anstrengungen unternommen, programmierbare Bausteine zu entwickeln, die es dem Anwender erlauben, eigene Logikfunktionen zu implementieren. Erste Ansätze dazu waren PALs und GALs, in denen bereits kleine Logikschaltungen untergebracht werden konnten.

Heute sind solche programmierbaren Bausteine, sogenannte CPLDs, mit über 10 000 Gattern erhältlich. Der Hauptvorteil dieser Bausteine ist, daß bedingt durch den inneren Aufbau nur sehr kurze und berechenbare Laufzeiten zwischen Ein- und Ausgängen des ICs entstehen. Allerdings bedingt der innere Aufbau von CPLDs auch, daß nur Schaltungen bestimmter Komplexität in einem Baustein untergebracht werden können. Diesen Nachteil hätte man auf Kosten größerer Laufzeiten durch eine höhere Anzahl an CPLDs ausgleichen können, jedoch waren zum Zeitpunkt der Überlegungen hauptsächlich Bausteine verfügbar, die zum Programmieren spezielle Programmiergeräte benötigen.

Dies jedoch steht im Gegensatz zu einer hohen Flexibilität: die Ausleseelektronik, die unter teilweise sehr beengten Bedingungen am Detektor untergebracht ist, kann unter Umständen nur unter hohem Zeitaufwand aus- und nach der Programmierung wieder eingebaut werden.

Aus diesen Gründen wurde von einem Einsatz von CPLDs in der RICH-Ausleseelektronik abgesehen.

#### 3.5.3 Microcontroller

Der Einsatz der heute von vielen verschiedenen Firmen erhältlichen Microcontroller wurde ebenfalls in Betracht gezogen. Diese Systeme sind zu günstigen Kosten verfügbar, frei programmierbar und bieten eine hohe Anzahl an Ein-/Ausgabemöglichkeiten an.

Wie man bei der im Kapitel 5 folgenden Beschreibung des RICH Readout-Controllers sehen wird, müssen von der Steuerlogik viele Aufgaben parallel und unabhängig voneinander erledigt werden. Dies bedingt entweder den Einsatz mehrerer Microcontroller, was

d.h. eine Lösung, die man fertig aus dem Regal des Herstellers zieht

sich in deutlich erhöhtem Platzbedarf der Komponenten niederschlägt, oder den Einsatz von Multitasking-fähigen Prozessoren. Die meisten heute erhältlichen Microcontroller sind jedoch nicht Multitasking-fähig oder müssen erst durch ein entsprechendes Betriebssystem diese Fähigkeit erhalten. Dies würde die Entwicklung eines gesamten Betriebssystems erfordern, was alleine den Rahmen einer Diplomarbeit deutlich übersteigen würde.

Ein weiteres Problem ist, daß die Steuerlogik z.B. auf dem Frontend-Modul wegen genau festgelegter zeitlicher Anforderungen mit minimaler Verzögerung auf Flanken von Steuersignalen reagieren muß. Betrachtet man einen hypothetischen Microcontroller mit einer Taktrate von 20 MHz (was einem heute erhältlichen typischen Microcontroller entspricht), so ergibt sich bei Abarbeitung eines Befehls pro Taktzyklus eine minimale Reaktionszeit von 50 ns, was jedoch beispielsweise für das T/H-Signal der Verstärker-Bausteine auf den Frontends zu langsam wäre: eine deutliche Verschlechterung des Meßergebnisses wäre die Folge.

Im RICH-Auslesesystem selbst wurde daher auf den Einsatz von Microcontrollern verzichtet. Jedoch finden diese Bausteine einen idealen Einsatzort in der Experiment-Steuerung und Überwachung (slow control), wo vielfältige Meß- und Regelaufgaben zu erledigen sind [29].

#### 3.5.4 **ASICs**

Bereits in der frühen Phase der HADES-Planung wurde der Einsatz von ASICs sowohl im analogen Frontend als auch für den digitalen Teil des Datenaufnahme-Systems in Erwägung gezogen [11, DIGIplex]. Jedoch hat man mittlerweile von solchen Überlegungen Abstand genommen, da der Einsatz von ASICs (speziell mit gemischten Analog-/Digital-Systemen) deutliche Nachteile im Vergleich zur jetzt eingesetzten Lösung gehabt hätte:

- Verlust von Flexibilität: das Aufnahmesystem ist in Art, Umfang und Timing festgelegt;

- Hohe Entwicklungskosten: das im ASIC zu integrierende System muß vor der Serienfertigung ausreichend getestet werden;

- Hohe Stückkosten: die zu erwartenden Entwicklungskosten teilen sich auf die letztendlich benötige Stückzahl von ca. 500 Stück auf.

ASICs mit gemischten Analog-Digital-Systemen sind bei HADES nur in Form von TD-Cs im Einsatz, wo durch die weitaus größere Verbreitung der TDCs in anderen Experimenten die Entwicklungskosten pro Stück gering gehalten werden konnten. Die RICH Ausleseelektronik verwendet auf den Frontends zur Analogverarbeitung ASICs in Form der GASSIPLEX-Chips, die am CERN aus den AMPLEX-ASICs [16] entwickelt wurden. Auch beim Preshower-Detektor werden Analog-ASICs zur Datenerfassung benutzt.

#### 3.5.5 FPGAs

Zeitgleich mit den ersten CPLDs wurde eine weitere Familie reprogrammierbarer Bausteine, die FPGAs, entwickelt, die ähnlich den CPLDs eine hohe Anzahl an Einzelgattern beinhalten, jedoch die Integration von Schaltungen höherer Komplexität erlauben. Erreicht wurde dies durch eine Änderung des inneren Aufbaus: das Innere eines FPGAs ist in eine Vielzahl von Logikblöcken aufgeteilt, die jeweils eine bestimmte Anzahl an logischen Verknüpfungen sowie Speicherelemente (Flipflops) enthalten. Zur Verbindung dieser von der Fa. Xilinx [30] CLB genannten Blöcke dient ein System von frei verschaltbaren Verbindungen. Die Verbindung zu den Anschlußpins erfolgt dabei über sogenannte IOBs, in denen ebenfalls Logikelemente untergebracht sind.

Als besonders nützlich hat sich die Möglichkeit erwiesen, FPGAs beliebig oft und ohne Ausbau aus der Schaltung neu konfigurieren zu können: auf diese Art und Weise konnten Korrekturen und neue Design-Ideen schnell verwirklicht und getestet werden. Die Programmierung der FPGAs erfolgte dabei über die VME-CPU.

Ebenfalls von Vorteil beim Übergang vom Prototyp zum Serienmodul des Readout-Controllers war die Möglichkeit, größere Bausteine (die über mehr interne Logikressourcen verfügen) anstelle der kleineren Modelle auf der Leiterplatte einzusetzen, ohne daß dabei Änderungen in der Leiterbahnführung notwendig waren. So konnten nach Abschluß der Fehlersuche (debugging) am Prototyp ohne Probleme zwei der bislang verwendeten FPGAs durch größere ersetzt werden, ohne daß die zu diesem Zeitpunkt bereits in Fertigung befindliche Leiterplatte geändert werden mußte (was zu größeren Kosten und Zeitverschub geführt hätte).

Allerdings ergeben sich durch den Einsatz von FPGAs auch einige Nachteile:

- Bedingt durch den inneren Aufbau muß beim Entwurf der Schaltungen verstärkt auf Laufzeiten zwischen einzelnen Funktionsblöcken geachtet werden und — wo immer möglich — auf den Einsatz von asynchronen Designs verzichtet werden. Dies allerdings führt generell zu deutlich stabileren Systemen und sollte auch beim Einsatz von CPLDs beachtet werden.

- Die verwendeten FPGAs der Firma Xilinx müssen nach jedem Einschalten neu programmiert werden. Dies führt zu einer Zeitspanne, in dem das Auslesesystem nicht verwendbar ist. Allerdings halten sich diese Zeiten in Grenzen, so daß hier der Vorteil, die Bausteine beliebig oft neu programmieren zu können, deutlich überwiegt.

- FPGAs der verwendeten Größenordnung sind im Vergleich zu CPLDs immer noch teurer. Durch die relativ kleine Stückzahl der zu bauenden Platinen fällt dieser Nachteil allerdings nicht allzu sehr ins Gewicht.

Die für die RICH-Ausleseelektronik getroffene Entscheidung, eine Mischung aus FPGAs und einigen Standardkomponenten zu verwenden, hat sich sowohl bei den Tests als auch ersten Einsätzen bei einer Teststrahlzeit als vorteilhaft erwiesen.

In den folgenden drei Kapiteln werden die einzelnen Module der RICH Ausleseelektronik vorgestellt sowie ihre Funktionsweise und das Zusammenspiel im Rahmen des Auslesesystems beschrieben. Dabei wird der Datenfluß "vom Detektor her" durch die Module erläutert.

# Kapitel 4

## Das RICH Frontend

### 4.1 Aufgaben

Das Frontend-Modul stellt das eigentliche Datenaufnahme-Modul im Auslesesystem des RICH dar. Die komplette Handhabung und Verarbeitung der Analogsignale, die aus den Photonendetektormodulen ausgelesen werden, sowie deren digitale Weiterverarbeitung in der LVL1-Pipe werden vom Frontendmodul übernommen. Im einzelnen müssen dabei folgende Aufgaben — zum Teil parallel und unabhängig voneinander — erledigt werden:

- analoge Signalverarbeitung: die Detektorsignale müssen verstärkt, differenziert und integriert (shaping), in eine T/H-Schaltung eingespeist und an den Eingangsbereich des ADC angepaßt werden.

- Analog/Digitalwandlung: die so vorbearbeiteten Signale müssen mit hoher Auf"—lösung und innerhalb einer festgelegten Zeit in Digitalwerte umgewandelt werden.

- Kanalzuordung: den so erhaltenen Digitalwerten müssen innerhalb eines Moduls eindeutige Kanalnummern zugeordnet werden.

- Schwellenvergleich: für jeden einzelnen Kanal muß ein Vergleich mit einer individuell einstellbaren Schwelle durchgeführt werden, um reale Signale vom Rauschen zu trennen und defekte Kanäle auszublenden.

- Mapping: die je nach Padplane andere Leiterbahnführung muß für jeden einzelnen Kanal getrennt durch Umordnen der Kanalnummern ausgeglichen werden.

- FIFO-Verwaltung: die Zugriffe auf die aus zwei FIFO-Bänken zusammengesetzte LVL1-Pipe müssen verwaltet werden.

- Auslesesteuerung: die Auslesezyklen zum Transportieren der Daten aus der LVL1-Pipe zur Bildverarbeitungseinheit und in die LVL2-Pipe (bzw. das Löschen der Daten) müssen vom Frontend-Modul gehandhabt werden.

• Busy-Handling: unterschiedliche Betriebs- und Ausnahmezustände im Frontend-Modul müssen mittels eines Busy-Signals dem Readout-Controller mitgeteilt werden.

Bei der Realisierung des Moduls sind jedoch einige Einschränkungen zu beachten: der verfügbare Platz, den ein einzelnes Frontend einnehmen kann, ist durch die Geometrie des Detektors festgelegt. Dies schränkt die Platinenfläche sowie die Anzahl und Größe der zu verwendenden Bauelemente stark ein; die Größe eines Frontend-Moduls ist auf 115·64mm² festgelegt.

Die analoge Signalverarbeitung stellt ebenfalls hohe Ansprüche an die Elektronik. Das unverstärkte Signal, das von den ladungsempfindlichen Vorverstärkern verarbeitet wird, entspricht Pulshöhen von ca. 10 mV. Um Verfälschungen durch Übersprechen von Signalen zu vermeiden, muß bis zum Einfrieren der Pulshöhe in den T/H-Stufen der GASSIPLEXe nach Möglichkeit jegliche Störquelle auf dem Frontend-Modul abgeschaltet sein. Da der Digitalteil des Frontends — bedingt durch die verwendeten Taktraten und schnellen Signalflanken — die größte Störquelle darstellt, muß dessen Aktivierung zeitlich genau auf die analoge Signalverarbeitung abgestimmt sein.

Das Frontend-Modul und seine Eigenschaften im analogen Teil (Auflösung, Linearität etc.) sind bereits mehrfach beschrieben worden [16], [17]. Im folgenden soll der Schwerpunkt auf den Digitalteil gelegt werden, der für den Einsatz am Experiment komplett neu gestaltet wurde. Diese Änderungen konnten dank der Flexibilität des FPGAs einfach und ohne Hardware-Modifikationen vorgenommen werden.

### 4.2 Blockschaltbild und Funktionsübersicht

Der prinzipielle Aufbau des Frontend-Moduls ist in Abbildung 4.1 dargestellt. Die einzelnen Funktionen sind dabei in Blöcken zusammengefaßt: der linke Block ist für die Analogverarbeitung zuständig. Je ein GASSIPLEX-Chip liefert über einen internen Multiplexer die in jeweils einer T/H-Stufe festgehaltenen Signalpegel von 16 Kanälen an einen Video-Multiplexer. Dieser schaltet eines der vier Eingangssignale auf einen einstellbaren Verstärker und führt das verstärkte Signal an den Eingang eines Analog-Digital-Wandlers. Dort endet der analoge Signalweg; alle weiteren Operationen werden mit den digitalisierten Daten durchgeführt.

Die beiden mittleren Blöcke beinhalten sämtliche Logikfunktionen zur Steuerung der Abläufe im Frontend. Dabei wurde eine strikte Trennung zwischen Datenaufnahme und Datenauslese vorgenommen; dies ermöglicht den asynchronen Ablauf beider Prozesse. Im oberen Funktionsblock enthalten sind Schwellenvergleicher, Mapping-Einheit und Triggertag-Speicher, die kontrolliert von einer Ablaufsteuerung vollautomatisch 64 Kanäle wandeln, den Vergleich mit den Schwellen und das Mapping durchführen und die so erhaltenen Daten zusammen mit dem Kontrollwort (dem Triggertag) in den LVL1-FIFOs ablegen. Die Steuerung dieser Ablaufsteuerung erfolgt nur mit Hilfe von LVL1-Triggerbefehlen.

Der untere Funktionsblock kontrolliert sämtliche Auslese- und Löschzyklen. Die Übertragung von Daten zur Ringerkennereinheit sowie in die LVL2-Pipe und die Löschung von Datensätzen werden hier durchgeführt.

Abbildung 4.1: Blockschaltbild des Frontend-Moduls. Die strikte Trennung zwischen Datenaufnahme und Datenauslese ermöglicht voll asynchronen Betrieb des Moduls.

Eine Sonderstellung nehmen in der Steuerlogik der Schwellenspeicher und die FIFO-Kontroll-Logik ein: der Speicher für die einzelnen Kanalschwellen wird in einem speziellen Zyklus von der Auslese-Ablaufsteuerung beschrieben, steht aber im normalen Betrieb nur der Datenaufnahmesteuerung lesend zur Verfügung. Die FIFO-Kontrolle überwacht das korrekte Beschreiben und Auslesen der LVL1-Pipe; insbesondere werden Ausnahmesituationen wie ein fast voller FIFO rechtzeitig erkannt und durch Erzeugung eines Busy-Signals an den Readout-Controller weitergemeldet.

Der rechte Funktionsblock enthält die zwei FIFO-Bänke zur Implementierung der LVL1-Pipe sowie alle zur Anpassung an den Modulbus notwendigen Bauelemente wie Datenbustreiber und Pegelwandler. Die Steuerung dieser Bauelemente wird von beiden Ablaufsteuerungen übernommen. Der Anschluß des Moduls an den Frontend-Bus erfolgt über den Busstecker, dessen Pinbelegung in Tabelle 4.1 angegeben ist. Das Layout des Frontend-Moduls ist in Abbildung 4.2 zu sehen.

Im folgenden wird genauer auf die unterschiedlichen Betriebsmodi des Frontendmoduls eingegangen. Dabei werden sowohl die internen Abläufe im Modul selber wie auch die dafür notwendigen Steuer- und Statussignale eingeführt und erklärt.

## 4.3 Digitalisierung und Zwischenspeicherung

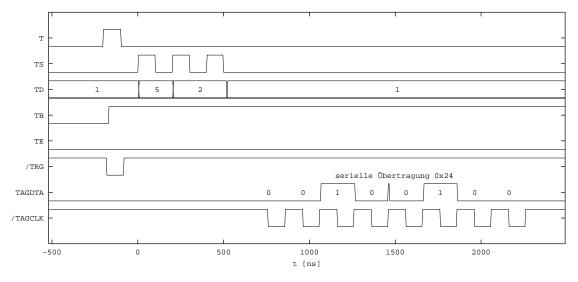

Die Datenaufnahme in den einzelnen Frontendmodulen wird über einen entsprechenden Befehl am LVL1-Triggerbus ausgelöst. In der DTU wird bei Eintreffen dieses Triggerkodes das Triggersignal /TRG erzeugt, das über den "Private Bus" genannten Teil des VME-Busses und den Readout-Controller an alle angeschlossenen Frontendmodule verteilt wird.

Abbildung 4.2: Layout des RICH Frontend-Moduls. Die Aufteilung in Funktionsblöcke entspricht der in Abbildung 4.1, lediglich die beiden Ablaufsteuerungen sind hier in einem Block zusammengefaßt.

Zum Zeitpunkt des Eintreffens von /TRG am Frontend ist der Digitalteil fast vollständig abgeschaltet, d.h. auch die später zur Datenaufnahme benötigte Taktquelle ist außer Betrieb. Das Frontend reagiert in diesem Betriebsmodus nur auf einlaufende Triggersignale und auf Auslese- und Löschzyklen. Dies reduziert den Anteil an elektronischem Rauschen und Übersprechen von Signalen auf das Analogsignal erheblich und ermöglicht erst die Aufnahme von korrekten Daten. Der Ablauf eines kompletten Datenaufnahmezyklus ist in Abbildung 4.3 zu sehen.

Die negative Flanke des /TRG-Signals setzt das T/H-Signal, das alle vier GASSIPLEX-Chips in den Hold-Modus schaltet. Damit ist das analoge Signal eingefroren; nun erst wird der für die weitere Ablaufsteuerung notwendige externe Quarz-Oszillator über die Steuerleitung SYSCLKON eingeschaltet. Davon ausgehende Störungen können das bereits gespeicherte und verstärkte Analogsignal nicht mehr verfälschen, jedoch muß wegen der nun stark erhöhten Störabstrahlung (die sich bei Digitallogik mit schnellen Signalflanken prinzipiell nicht vermeiden läßt) bei der weiteren Bearbeitung der Analogdaten durch geschicktes Timing die störenden Einflüsse möglichst klein gehalten werden. Zeitgleich mit dem T/H-Signal wird ein Busy-Signal (BUSY) erzeugt, das während der gesamten Wandlung gesetzt bleibt. Die Busy-Signale aller Frontends eines Readout-Controllers werden über ein Oder-Gatter logisch verknüpft und über die DTU an die CTU weitergeleitet. Somit bestimmt das "langsamste" Frontend die Länge des Busy-Signals und verhindert damit effektiv das Einlaufen weiterer Trigger während der Totzeit.

Alle zur jetzt ablaufenden Analog-Digitalwandlung notwendigen Signale werden durch die Aufnahme-Ablaufsteuerung erzeugt. Getaktet wird dieser Schaltungsteil mit 33,33 MHz über die Leitung SYSCLK. Bei dieser Taktfrequenz kann die geforderte Maximaltotzeit von  $10 \,\mu s$  eingehalten werden, eine Verkürzung der Totzeit durch Erhöhung des Taktes

| Signalname | Richtung | Pins |            | Richtung | Signalname |  |

|------------|----------|------|------------|----------|------------|--|

| /SBUSY     | out      | B1   | A1         | in       | /TRG       |  |

| /TAGCLK    | in       | B2   | A2         | in       | TAGDTA     |  |

| FC1        | in       | В3   | A3         | in       | FC0        |  |

| FC3        | in       | В4   | A4         | in       | FC2        |  |

| /STRBO     | out      | В5   | <b>A</b> 5 | in       | /STRBI     |  |

| n.c.       | -        | В6   | A6         | out      | /SMACK     |  |

| GND        | -        | В7   | A7         | -        | GND        |  |

| SD1        | bi       | В8   | <b>A</b> 8 | bi       | SD0        |  |

| SD3        | bi       | В9   | A9         | bi       | SD2        |  |

| SD5        | bi       | B10  | A10        | bi       | SD4        |  |

| SD7        | bi       | B11  | A11        | bi       | SD6        |  |

| SD9        | bi       | B12  | A12        | bi       | SD8        |  |

| SD11       | bi       | B13  | A13        | bi       | SD10       |  |

| SD13       | bi       | B14  | A14        | bi       | SD12       |  |

| SD15       | bi       | B15  | A15        | bi       | SD14       |  |

| +5V        | -        | B16  | A16        | -        | +5V        |  |

| +3.3V      | -        | B17  | A17        | -        | +3.3V      |  |

| GND        | -        | B18  | A18        | -        | GND        |  |

| GND        | -        | B19  | A19        | -        | GND        |  |

| -3.3V      | -        | B20  | A20        | -        | -3.3V      |  |

| -5V        | -        | B21  | A21        | -        | -5V        |  |

| GND        | -        | B22  | A22        | in       | SPULSER    |  |

| XDIN       | in       | B23  | A23        | out      | XDOUT      |  |

| XDONE      | out      | B24  | A24        | in       | XCCLK      |  |

| /XINIT     | bi       | B25  | A25        | in       | /XPRG      |  |

Tabelle 4.1: Pinbelegung des Frontend-Bussteckers. Die Signalrichtungen sind aus Sicht des Moduls angegeben, die Konfigurationssignale für die FPGAs in kursiver Schrift gesetzt.

ist möglich, erfordert aber den Neuentwurf des im FPGA implementierten synchronen Designs.

Die GASSIPLEX-Chips werden durch die Signale T/H\_TTL, CLK\_TTL und RES\_TTL angesteuert:

- T/H\_TTL steuert die T/H-Stufen an.

- CLK\_TTL bedient die GASSIPLEX-internen Multiplexer. Mit jedem Puls schaltet der GASSIPLEX einen Kanal weiter, nach 16 Pulsen steht am Ausgang wieder Kanal #0 an.

- RES\_TTL setzt die interne Logik (Multiplex-Zähler etc.) des GASSIPLEX zurück.

Der Videomultiplexer vom Typ EL4441CS [8] wird über die Signale MUXA1 und MUXA0

gesteuert: das binär kodierte Signal wählt den entsprechenden Eingang des Multiplexers aus.

Zur Analog-Digital-Wandlung wird ein ADC vom Typ ADS820 [5] eingesetzt. Dieser ursprünglich für Video-Anwendungen entwickelte Chip wird nur über das Signal ADCCLK angesteuert. Der ADC folgt dem Eingangssignal, solange ADCCLK high ist; bei der negativen Flanke wird das Signal in einen analogen Hold-Speicher übernommen und, während ADCCLK low ist, in ein 10 bit Digitalwort gewandelt. Aufgrund der internen Pipeline-Struktur erscheint das Ergebnis der Wandlung aber erst sieben Taktzyklen später an den Ausgängen; dies muß bei der Ansteuerung berücksichtigt werden.

Die 16 Kanalinhalte jedes einzelnen der 4 GASSIPLEXe werden durch ein Multiplex-Verfahren sequentiell an den Eingang des Videomultiplexers geführt. Der genaue Ablauf dieses Verfahrens ist in Abbildung 4.4 zu sehen: Über die Signale MUXA1 und MUXA0 wird der GASSIPLEX-Chip ausgewählt, mit CLK\_TTL wird der Kanal des einzelnen GASSI-PLEX an seinen Ausgang geschaltet. Dies hat den Vorteil, daß man die maximal mögliche Wandelfrequenz des ADC von 20MHz nutzen kann, ohne die GASSIPLEXe zu übertakten. Diese Art des Multiplexing ermöglicht erst das Einhalten der Totzeit von  $10~\mu s$ .

Die so erhaltenen digitalisierten Pulshöhen werden in den Xilinx FPGA geführt. Dort findet der Schwellenvergleich zeitgleich mit dem Mapping statt: der Schwellenspeicher ist als 16 bit breites SRAM ausgelegt; die unteren 10 bit werden als Schwellenwert zum Vergleich herangezogen, die oberen 6 bit ergeben die zuzuordnende Kanalnummer. Die Daten werden zusammen mit der Kanalnummer aus dem FPGA an die Dateneingänge beider FIFO-Bänke geführt; bei einem positiven Vergleich (d.h. der Analogwert ist höher als die Schwelle) wird ebenfalls ein Schreibsignal (/PWR und /AWR) erzeugt. Da zum Vergleich mit den einlaufenden Analogdaten ein echter Größenvergleich durchgeführt wird, ist es durch Setzen einer Kanalschwelle von 1023 möglich, den betreffenden Kanal komplett abzuschalten. Somit können defekte oder nicht benötigte Kanäle einfach und ohne Modifikation an der Hardware abgeschaltet werden.

Das Frontend kann zur besseren Abstimmung auf die IPU auch um einen eigenen Schwellebvergleicher für die Pattern-Daten erweitert werden; ob dies notwendig ist, kann allerdings erst nach intensiven Tests während einer Strahlzeit entschieden werden.

Während der im Frontend laufenden Wandlung wird von der DTU das mit dem vorhergegangenen LVL1-Befehl¹ eingetroffene Triggertag auf seriellem Weg über die Leitungen /TAGCLK und TAGDTA an die Frontends übertragen und dort in einem Register zwischengespeichert. Nach Wandlung aller 64 Frontendkanäle wird dieses Triggertag als letztes Wort in beide FIFO-Bänke geschrieben. Um die zu einem Subevent gehörenden Daten vom nächsten Datensatz abzugrenzen, wird das Triggertag auf besondere Art und Weise markiert: Jede FIFO-Bank ist aus zwei parallelgeschalteten FIFOs mit jeweils 9 bit Breite aufgebaut. Es ergeben sich also zwei FIFO-Bänke mit jeweils 18 bit Breite. Bei normalen Datenworten werden Bit 17 und 16 jeweils auf Null gesetzt, bei einem Triggertag hingegen wird Bit 17 (das ENDBIT) auf high gesetzt. Die Auslesesteuerung nutzt diese Zusatzinformation, um das Ende eines Datensatzes zu ermitteln.

<sup>&</sup>lt;sup>1</sup>nähere Informationen zur RICH DTU siehe Kapitel 6

Nach Abschluß der Wandlung werden die GASSIPLEXe über einen Puls auf RES\_TTL zurückgesetzt, das BUSY-Signal zurückgenommen und der Taktgenerator über SYSCLKON ausgeschaltet. Das Frontend ist nun wieder für einen neuen Datenaufnahme-Zyklus bereit.

# 4.4 Auslese der Frontend-Module

#### 4.4.1 Der Frontend-Bus

Um die in der LVL1-Pipe des Frontends gespeicherten Daten auszulesen, werden von der RICH DTU sowohl LVL1- als auch LVL2-Triggerbefehle ausgewertet und in entsprechende Auslesezyklen am Readout-Controller umgesetzt. Bedingt durch die Verkettung mehrerer Frontend-Module zu einer Gruppe wurde die Einführung eines Bussystems notwendig, dessen Grundfunktionen im folgenden beschrieben werden.

Das Bussystem der Frontends orientiert sich an gängigen Bussystemen, ist jedoch in einigen Punkten an die speziellen Anforderungen der Auslese angepaßt: so fehlen Adreßleitungen zur Adressierung einzelner Module. Um das System einfach skalierbar zu halten, wurde statt einer Einzelmodul-Adressierung eine Verschaltung über daisy chaining gewählt.

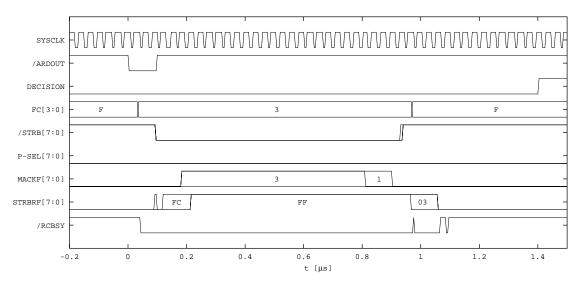

Prinzipiell kann der Bus in zwei verschiedenen Arten betrieben werden: